单片三维集成是集成电路在后摩尔时代的重要发展方向,存储与逻辑的单片集成可以大幅提升系统的带宽与能效,是解决当前集成电路领域面临的“存储墙”与“功耗墙” 挑战的主要技术路径。此外,硅基工艺的高热预算限制了其在后道工艺中实现有源器件的制备,因此硅基后道兼容、低热预算、高性能的新型半导体沟道成为了学术界和工业界的前沿热点领域。以铟镓锌氧化物(IGZO)为代表的非晶氧化物半导体具有极佳的综合性能,是后道兼容逻辑器件与存储器件的主要候选材料。

吴燕庆研究员-黄如院士团队在过去五年中面向单片三维集成中的半导体材料、界面、输运、器件、电路与关键集成技术开展了系统研究。经过数年攻关,突破了非晶氧化物半导体在尺寸微缩时面临的材料、工艺与器件瓶颈。团队实现的器件与电路在各方面性能上均达到了国际最高水平,填补了先进集成电路领域在该方向上的空白,并建立了具有自主知识产权的非晶氧化物半导体成套关键技术。在近日召开的第68届国际电子器件大会IEDM中,团队在先进逻辑器件、存储器技术、新型器件技术等session共入选5篇论文,其中两篇报道了团队关于非晶氧化物半导体在逻辑与存储方面的最新成果。

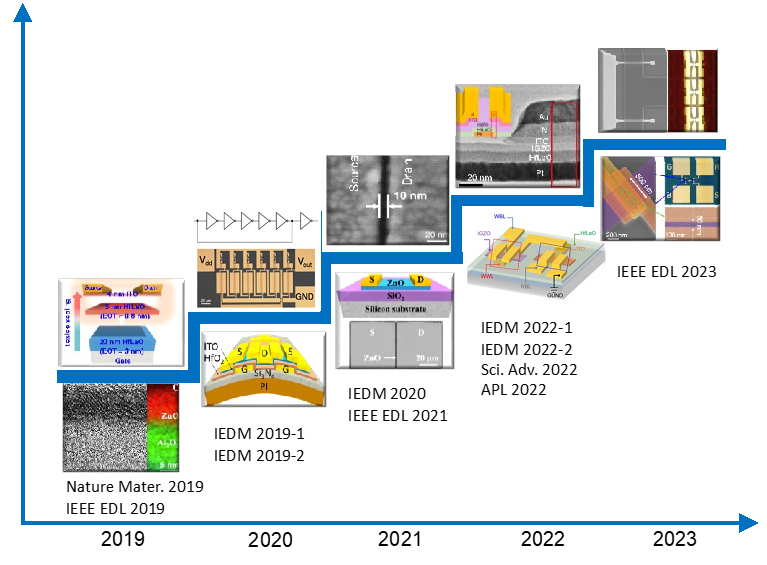

图1.近五年团队在氧化物半导体器件方面的代表性工作

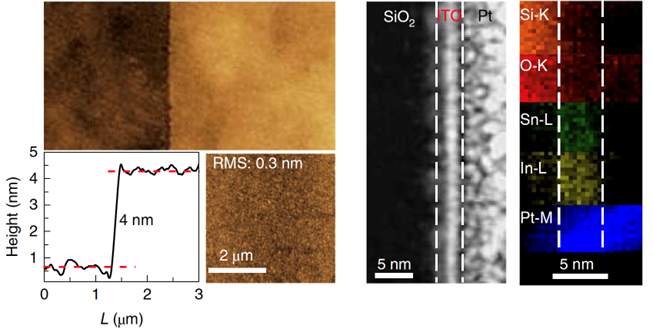

长久以来,研究最为广泛的IGZO氧化物半导体的迁移率停留在10cm2/Vs左右,如何进一步提升迁移率是一直以来该领域的主要挑战之一。针对上述挑战,团队在原子层沉积ALD工艺与物理气相沉积PVD工艺两个方面均开展了系统研究。在ALD生长方面,优化了超薄非晶氧化物半导体沟道的ALD生长工艺,成功实现了10纳米的超薄沟道, 迁移率提升至43 cm2/Vs,并系统研究了器件在180oC高温下的工作特性。该工作实现了国际同类器件中最薄的ZnO沟道、最高的迁移率与器件开关比 (IEEE EDL 40, 3, 419-422, 2019; IEEE EDL 42, 5, 716-719, 2021);在PVD 生长方面,优化了超薄非晶氧化物半导体的磁控溅射工艺,结合ALD生长的高质量HfLaO介质,成功将3.5纳米超薄沟道中的迁移率大幅提升至60 cm2/Vs左右。在国际上首次提出了通过量子限域效应将金属性氧化铟锡ITO转变为宽禁带半导体性的突破性方法,与之前同类器件相比实现了相同关态特性下开态性能的全面大幅超越(Nature Mater. 18, 1091-1097, 2019)。

图2.超薄氧化物半导体的材料特性基本表征

图2.超薄氧化物半导体的材料特性基本表征

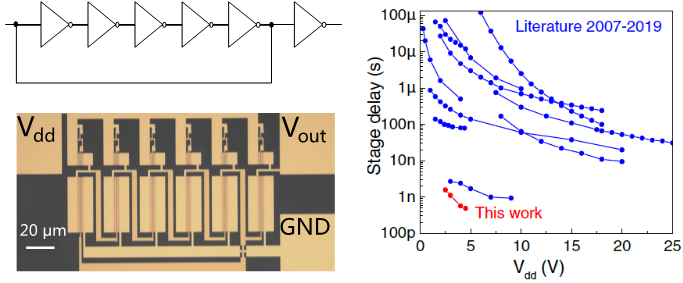

氧化物半导体在当前主要应用于显示面板的驱动器件,特征尺寸为数十微米,与集成电路器件的特征尺寸存在上千倍的差距,如何进一步缩短沟长并提升性能是该技术跨入集成电路领域面临的主要挑战。针对上述挑战,团队系统开展了氧化物半导体器件在尺寸微缩下的性能优化研究,实现了10纳米超短沟长、1纳米超薄EOT栅介质与阈值电压的可控正移,关态电流、开关比等方面超越国际同类器件十倍以上。研究了非晶氧化物半导体在超短沟道下的输运机制,首次实现了弹道输运,效率高达68.4%。器件开态电流在国际上首次突破1mA/μm,跨导大于1000μS/μm,超过同类器件5倍以上。短沟道效应漏致势垒降低(DIBL)仅为同样厚度硅基SOI器件的一半。器件的截止频率与最大振荡频率达国际最高水平。在逻辑电路方面,实现了高性能的环形振荡器电路,单阶延迟为0.4 ns,超越之前同类器件两倍以上(IEDM 3.5.1-3.5.4, 2019,IEDM 40.5.1-40.5.4, 2020)。上述两项进展均为当年IEDM先进逻辑session唯一来自大陆的工作。

图3.基于超薄氧化物半导体的环形振荡器结构与电学特性

图3.基于超薄氧化物半导体的环形振荡器结构与电学特性

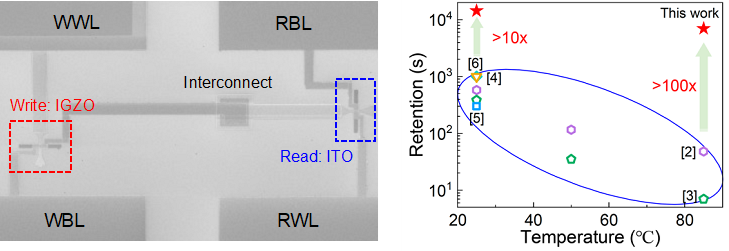

相比已经发展至3纳米节点的硅基集成电路器件,氧化物半导体的显著特点在于其宽禁带特性导致的极低关态漏电流,因此在DRAM应用中对于提升数据保持时间和降低功耗具有极大的优势,但当前面临的主要问题在于氧化物半导体高阈值电压与高开态电流不可兼得,从而需要负保持电压来实现高数据保持时间,并且写入速度仍然远低于主流DRAM的水平。针对上述问题,团队针对性开展了沟道优化与欧姆接触优化研究,通过原位氧离子处理的方式实现了兼具低载流子浓度与高迁移率的非晶氧化物半导体沟道。提出了采用ITO(铟锡氧化物)作为接触中间层降低金属接触势垒高度的有效方法,获得了低至278Ω·μm的接触电阻,达到国际最优水平。所制备的IGZO器件实现了国际最高的跨导(637 μS/μm)与开态电流(1207 μA/μm),其中开态电流是此前文献报道最高电流的2倍,器件开关比高达1011(IEDM 2.7.1-2.7.4, 2022),实现了阈值电压在100 pA*W/L的标准下大于1.2 V,同时输出电流在过驱动电压为1 V情况下达到24 μA/μm,栅压为0时的关态电流在常温和85 oC下均小于10-19 A/μm,为国际最优水平。所构建的2T0C DRAM单元成功实现了10 ns的超快写入速度,以及断电情况下室温大于10 ks、85 oC下大于7 ks的数据保持时间,分别为之前同类工作的10倍与100倍。此外,通过调节写入管的字线和位线电压,成功在常温和85 oC下实现了具有超高区分度和线性度的3-bit存储,并可通过电压协同调节进一步扩展存储容量,展示了非晶氧化物半导体在大容量、高密度、非易失三维集成DRAM方向的应用潜力(IEDM 26.6.1-26.6.4, 2022)。

图4.基于超薄氧化物半导体的2T0C DRAM结构与电学特性

图4.基于超薄氧化物半导体的2T0C DRAM结构与电学特性

当前,国际上普遍认为下一代DRAM技术主要发展方向是通过三维堆叠从而提升存储密度,氧化物半导体具备的独特低热预算特性使其在单片三维集成应用中极具潜力。针对三维集成关键工艺缺乏、应力导致沟道性能退化等问题,团队系统研究了低热预算下的高性能非晶氧化物半导体器件。在柔性聚酰亚胺衬底上制备了160nm沟长的柔性射频器件,实测截止频率为2.1GHz,最大振荡频率为3.7GHz,性能为之前同类器件10倍以上。该器件在10mm弯曲半径下弯折五万次,在1mm弯曲半径下弯折一千次,其直流与射频特性仍能保持正常工作状态,验证了其优异的应力特性(IEDM 8.2.1-8.2.4, 2019)。在表面粗糙度优化后的减薄聚酰亚胺衬底上进一步将沟道长度微缩为15纳米,实现了国际最高水平的截止频率11.8GHz,最大振荡频率达15GHz,首次实现了该类器件在4.3K和380K下的稳定工作(Sci. Adv. 8, eade4075, 2022)。

近五年,吴燕庆研究员-黄如院士团队在基于新型半导体沟道器件的先进逻辑器件、存储器件与射频器件方面累计发表Nature Nanotechnology、Nature Materials、Nature Electronics、Nature Communications、Science Advances与IEDM等30余篇。研究工作在国际上形成重要影响力,引起了包括英特尔、台积电在内的工业界的广泛关注与多次引用。

以上论文的相关研究工作得到了国家基金委创新群体、国家基金委重大项目、科技部国家重点研发计划、高等学校学科创新引智计划等项目的资助,以及国家集成电路产教融合创新平台、微纳电子器件与集成技术全国重点实验室、集成电路高精尖创新中心、集成电路科学与未来技术北京实验室等基地平台的支持。