被誉为集成电路领域“国际奥林匹克盛会”的国际固态电路会议(International Solid-State Circuits Conference, ISSCC)受新冠病毒疫情影响于2021年2月13日至22日以线上会议形式举办,本次会议是该系列会议的第68届。微纳电子学系在“超低功耗智能物联网芯片(AIoT)”、 “高性能雷达频率源”等高端芯片领域取得重要进展,相关成果在ISSCC上报道。

1. 异步事件驱动型AIoT唤醒芯片

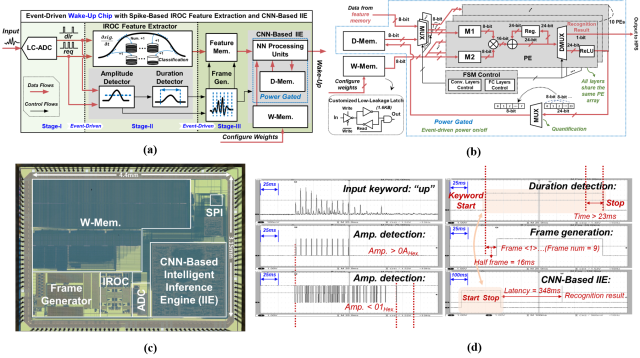

面向智能物联网(AIoT)对低功耗唤醒芯片的迫切需求,北京大学黄如院士-叶乐副教授课题组,与浙江省北大信息技术高等研究院、浙江大学、上海芯翼信息科技有限公司合作,提出了国际首创的异步事件驱动型AIoT芯片架构,解决了在随机稀疏应用场景下长时平均功耗高的问题,显著降低了AIoT节点设备的功耗;课题组同时提出了异步脉冲的信号特征提取方法,仅以几十nW的极低功耗代价便实现了信号特征提取;不仅如此,基于“时域帧生成器”和“卷积神经网络”智能推断引擎的技术,结合重训练机制,在具备低功耗的同时,使物联网应用场景因噪声而导致推断精度低的问题得以解决。

图1. (a)异步事件驱动型AIoT芯片架构, (b)卷积神经网络电路架构, (c)芯片显微照片,

(d)语音关键词唤醒测试波形

基于上述创新技术,课题组研制了一颗国际上功耗最低的通用型AIoT唤醒芯片,长时待命(on-call waiting for events)功耗仅148nW,可供5mm纽扣电池(2mAh)使用5年,芯片演示应用结果显示:语音关键词识别率达94%,异常心电图识别率达99%;为国际迄今为止首次且唯一的“异步事件驱动型AIoT芯片”,该工作为未来实现基于全异步脉冲神经网络(A-SNN)的AIoT芯片奠定了基础。

该工作以《基于异步脉冲特征提取和卷积神经网络的148nW通用事件驱动AIoT智能唤醒芯片》(A 148nW General-Purpose Event-Driven Intelligent Wake-Up Chip for AIoT Devices Using Asynchronous Spike-Based Feature Extractor and Convolutional Neural Network)为题,在2021年2月17日于国际固态电路峰会ISSCC线上发表,为前瞻技术领域Session 12(Innovations in Low-power and Secure IoT)的第一篇文章,被遴选为Highlight亮点论文,也是ISSCC前瞻技术领域(TD,Technology Direction)国内首次且唯一的Highlight亮点论文,也是今年前瞻技术领域国内唯一发表论文。

相关研究工作得到了国家优秀青年科学基金、国家重点研发计划等项目的资助,以及浙江省北大信息技术高等研究院、浙江大学、上海芯翼信息科技有限公司等平台的支持。

2. 动态电荷域CMOS湿度/电容传感芯片

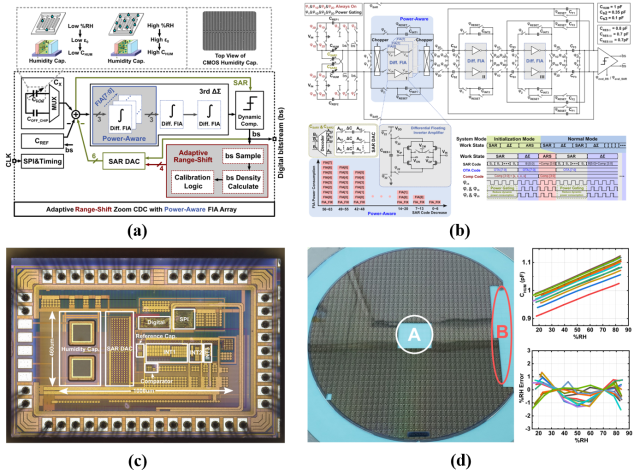

面向高能效、高精度的物联网传感器应用需求,北京大学黄如院士-叶乐副教授课题组,与浙江大学、浙江省北大信息技术高等研究院合作,提出了国际领先的动态电荷域电容传感技术,具有国际领先的传感精度,在实现高精度的同时显著降低了物联网传感节点的功耗;课题组同时提出了基于动态范围自适应滑动技术(Adaptive Range-Shift, ARS)的缩放型(Zoom)电容数字转换器(Capacitance-to-Digital Converter,CDC),解决了Zoom架构中冗余过大造成的精度损失和抗片外寄生/干扰能力差的问题;还提出了基于功耗自感知技术(Power-Aware)的悬浮反相器型放大器阵列,解决了兼容不同传感终端所带来的能效损失问题,显著延长了多应用兼容传感芯片的电池使用寿命。

图2. (a)动态电荷域电容传感芯片架构图, (b)电路原理图及工作时序图, (c)芯片显微照片,

(d)晶圆不同位置处的芯片、湿度及其误差测试曲线

基于上述创新技术,课题组研制了一颗国际上功耗最低的CMOS湿度传感芯片,平均功耗仅1.5μW,可供8mm纽扣电池(42mAh)使用4年,湿度检测分辨率高达0.0094%RH,电容检测精度高达17.9aF,综合性能指标FoM高达0.135pJ·%RH2,与当前世界最好水平相比,功耗降低了2倍,综合性能指标FoM提升了6倍。

该工作以《基于自适应范围滑动的缩放型电容数字转换器和功耗自感知悬浮反相器型放大器阵列的1.5μW和0.135pJ·%RH2的CMOS全集成湿度传感器芯片》(A 1.5μW 0.135pJ·%RH2 CMOS Humidity Sensor Using Adaptive Range-Shift Zoom CDC and Power-Aware Floating Inverter Amplifier Array)为题,在2021年2月16日于国际固态电路峰会ISSCC线上发表,为前瞻技术领域Session 5(Analog Interface)的第一篇文章,并被遴选为Highlight亮点论文,并参与了Demo Session的演示系统展示。该论文为ISSCC模拟电路领域(ANA, Analog)国内首次且唯一的Highlight亮点论文,也是今年模拟电路领域国内唯一发表论文。

相关研究工作得到了国家优秀青年科学基金、国家重点研发计划等项目的资助,以及浙江大学、浙江省北大信息技术高等研究院等平台的支持。

3. 高性能雷达频率源芯片

针对自动驾驶、小型无人机及先进制造业等对低成本、小型化毫米波雷达的迫切需求,北京大学廖怀林教授-刘军华副教授课题组提出了全数字频率源架构,开发了高精度数控振荡器、数字相位插值器、宽带线性校正算法等系列数字化射频电路技术。

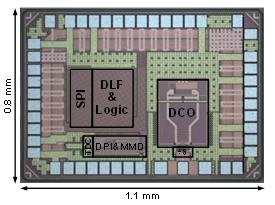

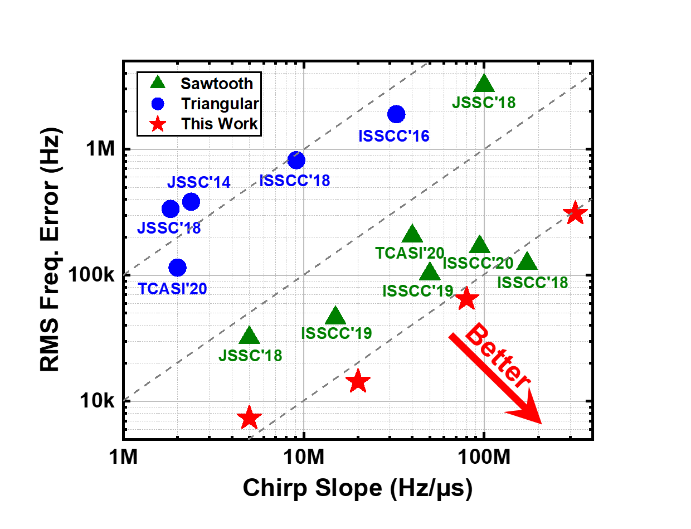

基于上述创新技术,课题组研制出一款面向毫米波调频雷达应用的24GHz调频连续波频率综合器芯片,该频率综合器采用全数字架构,辅以先进的自适应校准算法,刷新了当前同波段下调频带宽(3.2GHz@24GHz)和调频速率(320MHz/μs)的世界纪录,且调频过程中最小频率均方根误差仅7.35kHz,也是同类最优水平。

图3 高性能雷达频率源芯片照片与调频性能

该工作以《24GHz频段3.2GHz连续扫频带宽320 MHz/μs扫频速度0.01%频率均方根误差的基于自校正全数字锁相环的调频连续波频率综合器》(A 24GHz Self-Calibrated ADPLL Based FMCW Synthesizer with 0.01% rms Frequency Error under 3.2GHz Chirp Bandwidth and 320 MHz/μs Slope)为题,在2021年2月18日于国际固态电路峰会ISSCC线上发表,在频率综合器的Session 32(Frequency Synthesizers)专题论坛上收录。

会议背景介绍:

ISSCC会议每年2月中旬在美国旧金山召开,是国际公认的规模最大、领域内最权威、水平最高的芯片设计领域学术会议,有着集成电路“奥林匹克盛会”的美誉。历史上入选ISSCC的论文都代表着当前全球顶尖水平,展现出芯片技术和产业的发展趋势,多项“芯片领域里程碑式发明”均在ISSCC首次披露,如:世界上第一个集成模拟放大器芯片(1968年)、第一个8位微处理器芯片(1974年)和32位微处理器芯片(1981年)、第一个1Gb内存DRAM芯片(1995年)、第一个多核处理器芯片(2005年)等等。