近日,EDA领域著名会议DATE 2023(欧洲设计自动化与测试会议)在比利时安特卫普召开,这是该会议疫情后首次恢复线下模式召开,学院学子赴比参加此次盛会,向国际同行展示了最新的研究成果并进行了深入的交流。在本届大会中,北京大学关于模拟集成电路版图自动布线的成果获得了最佳论文奖。

相比数字集成电路,模拟集成电路设计的自动化程度较低,特别是版图长期依赖于手工绘制。其中,布线需要完成引脚之间的互连,是版图设计中极其繁琐的步骤,而布线结果对模拟电路后仿性能影响很大。模拟电路布线不仅需要考虑复杂的几何约束,如满足各类设计规则、减少绕线弯折等,还需要考虑电学性能相关的约束,如电迁移、电压降和对称性等。如何在多种复杂约束下高效探索布线方案、减少人工干预,是模拟电路自动布线亟待解决的问题。

集成电路学院设计自动化与计算系统系/集成电路高精尖创新中心林亦波研究员和王润声教授团队,联合集成电路设计系多位师生,提出了多约束协同的模拟电路版图自动布线框架,并实现了工具原型SAGERoute,能够同时考虑复杂的几何与电学约束,自动求解满足约束的互连线宽,规划布线拓扑并完成连线。该布线工具在多个真实的流片案例上完成了验证,包括手工绘制布局的FIA和SAR-ADC等电路,涵盖了65nm、40nm和28nm三个工艺节点,能够在几十秒内完成布线,并达到接近设计专家手工布线的后仿性能。

该工作以《SAGERoute: Synergistic Analog Routing Considering Geometric and Electrical Constraints with Manual Design Compatibility》为题发表,博士生张昊懿与高笑涵为共同第一作者。

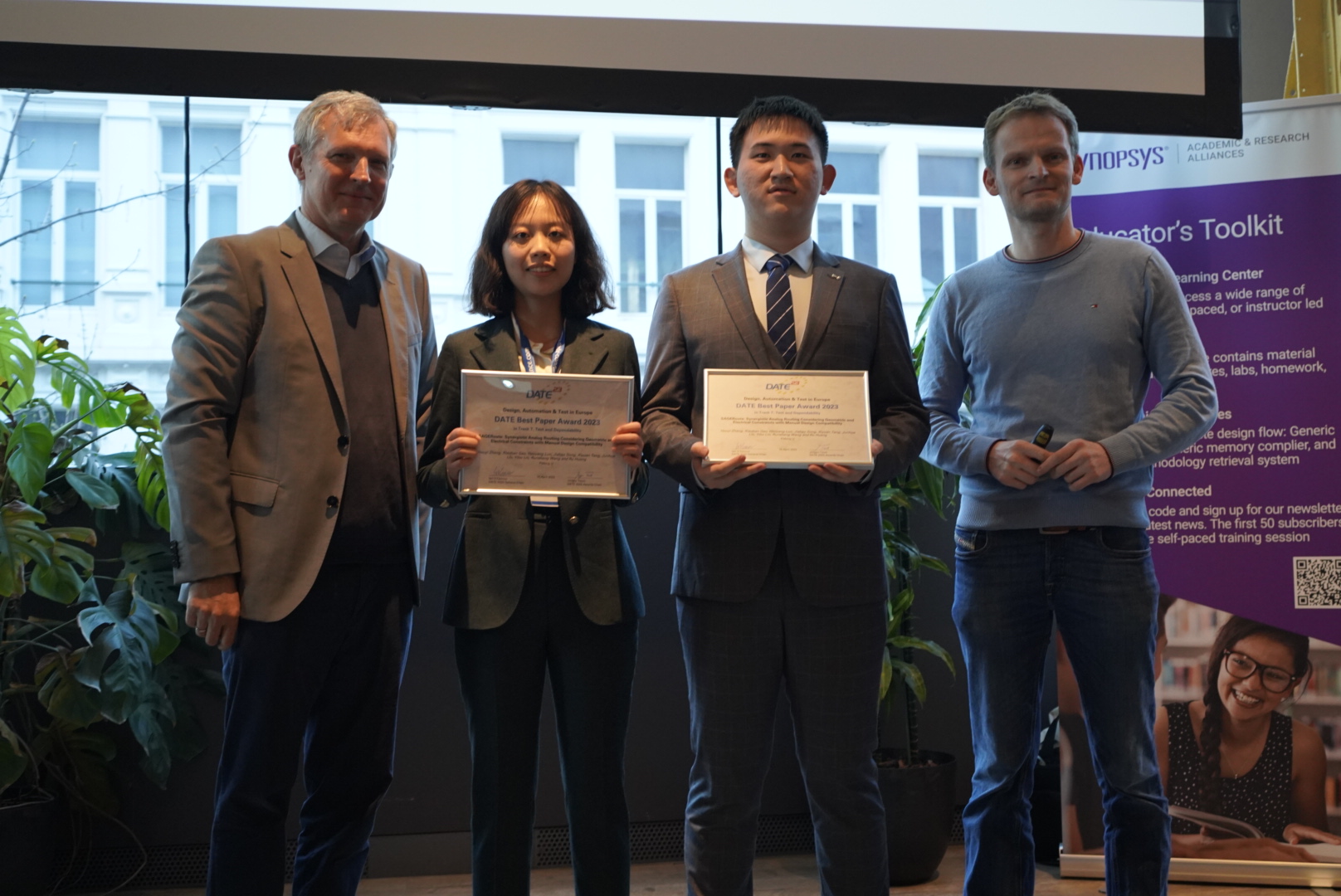

领奖合影

(从左往右为:大会Award主席Jürgen Teich,高笑涵,张昊懿,大会程序主席Robert Wille)

该工作得到了自然基金委重点项目“面向模拟集成电路敏捷设计的版图融合自动编译系统”等课题的支持。据悉,团队正在与概伦电子合作,将该成果作为模块集成到商用版图设计平台NanoDesigner中。

背景链接1:欧洲设计自动化与测试会议(Design, Automation and Test in Europe)由IEEE与ACM共同支持举办,是EDA领域的三大主要会议之一,具有重要的学术和产业影响力。会议分为D,A,T,E四个主题,分别关注电子系统设计方法与工具、应用设计、测试与可靠性、嵌入式系统设计。

背景链接2:设计自动化与计算系统系是国内高校唯一聚焦EDA技术的系,面向产业需求打造计算芯片与计算系统的跨领域人才培养体系,研究全流程EDA工具与自主标准、领域专用计算系统结构以及软件工具链等关键技术,并与国内外领先的企业深入合作,部分成果已经成功得到转化应用,相关技术是业内目前唯一的解决方案;同时,依托院系成立了无锡北京大学EDA研究院以及多个企业联合实验室,形成了教育、科技和人才协同发展的布局。