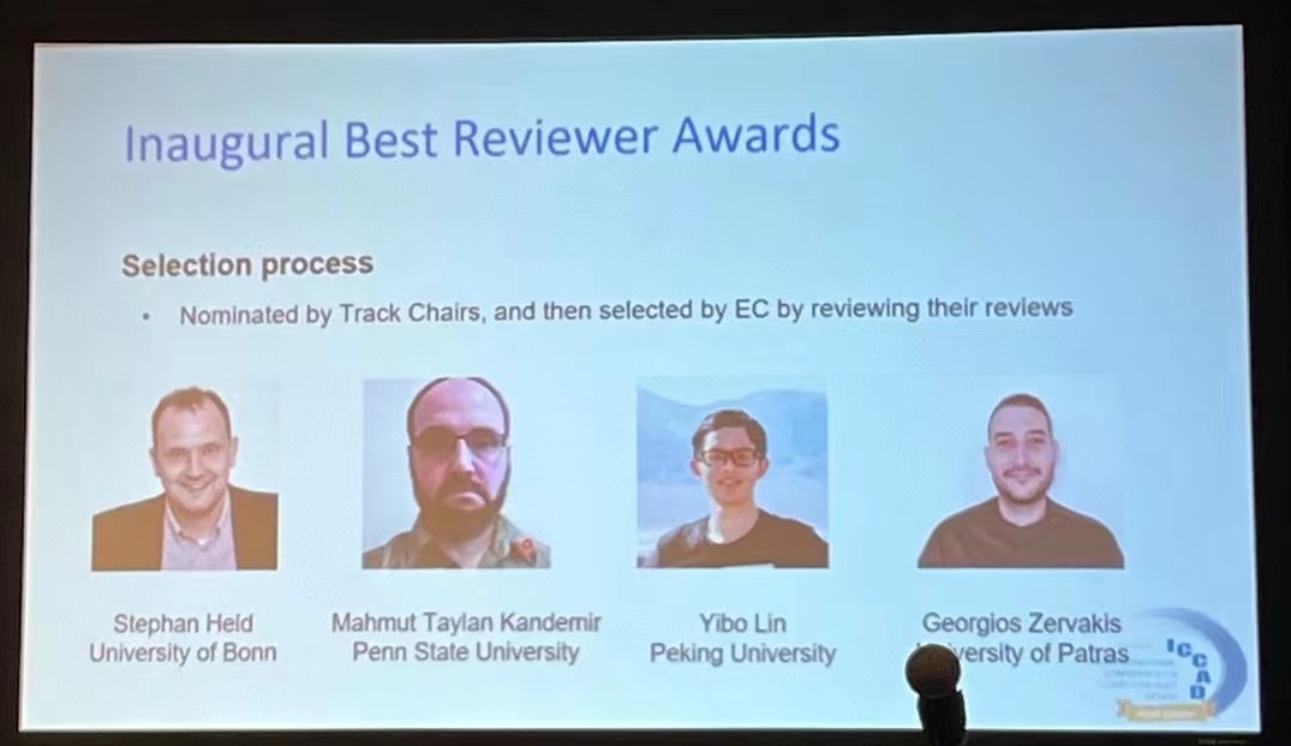

近日,以北京大学集成电路学院为第一完成单位的7篇论文在美国旧金山举行的第42届国际计算机辅助设计会议(ICCAD 2023)上发表,向国际电子设计自动化(EDA)领域的同行展示了北京大学最新的研究成果。这7篇论文内容涉及EDA算法和物理后端设计,人工智能调度、映射和加速器设计方法隐私计算等多个学术前沿领域。同时,学院梁云、林亦波、李萌等多位老师为会议TPC成员,林亦波、李萌等多位老师承担了Session Chair工作,林亦波研究员还获得了首届最佳审稿人奖。

图:林亦波研究员获得ICCAD首届最佳审稿人奖

论文的详情如下:

1. 考虑二阶信息的宏模块布局优化技术

宏模块布局是大规模集成电路物理设计中的关键环节,也是近年来备受关注的问题。由于宏模块占据了芯片版图大量面积,对最终设计的性能影响巨大。近年来,不少研究尝试利用人工智能或解析方法改进宏模块布局,这些方法都依赖混合尺寸布局引擎作为内核。然而,现有的混合尺寸布局内核存在稳定性差、不易收敛的问题。林亦波研究员团队提出了一种改进的混合尺寸布局引擎内核,实现鲁棒布局收敛和宏模块合法化,并在MMS、ISPD2005和TILOS测试用例上分别达到了6.5%、29.6%和33.3%的线长优化。通过将该内核集成到英伟达AutoDMP宏模块布局工具中,提高了帕累托前沿的搜索性能。该工作以《Stronger Mixed-Size Placement Backbone Considering Second-Order Information》为题发表(博士生陈一帆为第一作者,林亦波研究员为通讯作者)。

2. AI与异构计算加速物理设计优化技术

布线拥塞和时序是集成电路物理设计中关注的重要指标。随着设计复杂度增加,拥塞和时序问题日益凸显。传统基于CPU的拥塞和时序分析方法往往在8-16线程即达到饱和,难以通过增加CPU线程继续提升效率,导致设计优化效率低下。林亦波研究员团队提出利用AI建模技术和GPU异构并行加速拥塞和时序优化,并克服传统设计流程各环节之间的信息依赖。进一步在开源AI for EDA数据集CircuitNet上进行了验证,实现了高效拥塞和时序优化。该工作为ICCAD邀请报告,并以《Accelerating Routability and Timing Optimization with Open-Source AI4EDA Dataset CircuitNet and Heterogeneous Platforms》为题发表(博士生江循和郭资政为共同第一作者,林亦波研究员为通讯作者)。

3. 面向芯粒加速器成本效益感知的定制设计方法

基于芯粒技术的加速器可将若干定制化的裸片集成至同一封装内来提升能效并降低制造成本。论文提出一种成本感知的加速器设计方法,系统探索单芯粒架构与多芯粒集成的设计空间。我们开发了面向多芯粒的性能建模框架与基于机器学习的设计优化框架,能够在成本预算内为应用定制高性能加速器设计。该工作以《Monad: Towards Cost-effective Specialization for Chiplet-based Spatial Accelerators》为题发表(博士生郝晓辰为第一作者,梁云研究员为通讯作者)。

4. 面向各类存算设备统一的深度神经网络映射框架

该论文设计并实现了一个神经网络算子到多种存内计算设备的自动化映射框架。该框架的核心是提出了一个描述存内计算设备的计算和数据映射特性的硬件抽象,包括计算抽象和内存抽象两个部分。依据该抽象,我们对映射空间进行了系统定义,并可以自动化生成和探索映射空间。该工作以《ARES: A Mapping Framework of DNNs towards Diverse PIMs with General Abstractions》为题发表(博士生崔修萍为第一作者,梁云研究员为通讯作者)。

5. 可靠性增强的神经网络加速器数据流优化算法

随着近年来深度学习的快速发展,硬件加速器越来越多地应用于自动驾驶、机器人等安全关键的领域。然而,加速器通常采用先进的工艺节点制造来提高性能和能效,但也更容易受到工艺、电压、温度和老化(PVTA)变化的影响而产生时序错误。通过重新审视时序错误的物理来源,发现加速器中的大部分时序错误是由一种特定的输入模式导致的,我们称之为关键输入模式。为了提高加速器对于时序错误的鲁棒性,提出了一种可靠性增强的加速器数据流优化技术(READ),从而有效减少时序错误。READ通过探索将训练好的深度神经网络映射到加速器时的最优计算顺序,来减少关键输入模式的出现。在VGG和ResNet上的实验结果表明,READ平均将时序错误率(TER)降低7.8倍。该工作以《READ: Reliability-Enhanced Accelerator Dataflow Optimization using Critical Input Pattern Reduction》为题发表(张作栋博士后为第一作者,李萌研究员为通讯作者)。

6. 面向边缘设备的高效内存感知调度算法

在资源受限的边缘端设备上进行深度神经网络(DNN)推理时,考虑内存的网络调度变得越来越重要。然而,由于神经网络的拓扑结构十分复杂,考虑内存的调度变得非常具有挑战性。该论文提出了基于迭代计算图优化的高效考虑内存的调度框架,采用了一种迭代图融合算法,可以在保持调度最优性的同时简化计算图。进一步提出了一个整数线性规划模型,结合拓扑感知的变量剪枝,来高效地调度简化后的计算图。在不同的网络上评估了我们的方法与先前的算法的对比,并证明了该方法在所有的基准测试中都优于现有的技术,将峰值内存占用量降低了13.4%以上。该工作以《Memory-aware Scheduling for Complex Wired Networks with Iterative Graph Optimization》为题发表(博士生仲书璋为第一作者,李萌研究员为通讯作者)。

7. 面向轻量级神经网络的高效同态加密打包算法

轻量级神经网络,例如MobileNetV2,EfficientNet等,以轻量的计算实现了最先进的准确率。然而,现有的基于同态加密的两方计算框架并没有针对这些网络进行优化,导致了高昂的推理开销。因此,该论文提出了Falcon,一种针对基于同态加密的两方计算框架的有效的密集打包算法。Falcon采用了一种零感知的贪心打包算法和一种通信感知的算子切割策略,来提高逐深度卷积的打包密度。Falcon在算子级别较CrypTFlow2, Iron和Cheetah分别实现了超过15.6 倍,5.1 倍和1.8 倍的延迟降低。同时,在网络级别,Falcon 在Tiny Imagenet数据集上分别实现了4.2% 的准确率提升。该工作以《Falcon: Accelerating Homomorphically Encrypted Convolutions for Efficient Private Mobile Network Inference》为题发表(博士生许天识为第一作者,李萌研究员为通讯作者)。

背景链接1:

由电气电子工程师学会(IEEE)和美国计算机学会(ACM)共同举办的国际计算机辅助设计会议(ICCAD)被公认为EDA领域最重要的会议之一,享有很高的国际学术地位和广泛的影响力。该会议是探索EDA研究领域新挑战、展示前沿创新解决方案和识别新兴技术的重要论坛,涵盖了从器件和电路级到系统级的所有设计与自动化主题、以及后CMOS设计等新型方向。ICCAD 2023为第42届会议,于2022年10月29日至11月2日在美国旧金山举行。

背景链接2:

北京大学集成电路学院成立了国内首个聚焦EDA技术的“设计自动化与计算系统系”,打造先进的教学与人才培养体系,并与国内外领先的企业深入合作,部分成果已经成功得到转化应用,相关技术是业内目前唯一的解决方案;同时,依托院系新成立了北京大学无锡EDA研究院,加上之前与EDA及设计方向的头部企业共建的多个联合实验室,形成了教育、科技和人才三位一体的布局。