近日,第七十一届国际固态电路大会(ISSCC 2024)在美国旧金山隆重举行,业界誉其为“芯片设计国际奥林匹克”。北京大学集成电路学院部分师生赴美参加了此次盛会,并报告了各自方向的最新研究成果,与国际同行进行深入的学术交流。

在本届ISSCC上,北京大学集成电路学院/集成电路高精尖创新中心的相关研究成果获得了业内高度认可并取得多项成就:

1.黄如院士-叶乐教授团队荣获ISSCC 2023年度唯一最佳论文奖(杰出技术论文奖)(Anantha P. Chandrakasan Award for Outstanding Distinguished-Technical Paper),这既是集成电路设计领域国际年度最高学术荣誉,也是ISSCC自1953年创办70年以来国内(含港澳地区)首次获奖;博士生高继航同学为该论文的第一作者,沈林晓研究员和叶乐教授为通讯作者。(JihangGao, Linxiao Shen*, Heyi Li, Siyuan, Ye, Jie Li, Xinhang Xu, Jiajia Cui, Yunhung Gao, Ru huang, and Le Ye*, “A 7.9fJ/Conversion-Step and 37.12aFrms Pipelined-SAR Capacitance-to-Digital Converter with kT/C Noise Cancellation and Incomplete-Settling-Based Correlated Level Shifting”, ISSCC 2023)

图一 最佳论文奖颁奖现场

2.黄如院士-叶乐教授团队博士生李和倚获得2023-2024年度SSCS国际固态电路协会博士成就奖(2023-2024 SSCS Predoctoral Achievement Award),这是集成电路设计领域在读博士生全球最高学术荣誉,也是我校首位学生获奖;李和倚博士生导师为黄如院士,指导教师为叶乐教授。

图二 博士生李和倚颁奖现场

3.此次共有5篇高水平论文入选,研究成果覆盖了人工智能芯片(2篇)、数模混合芯片(2篇)、模拟芯片(1篇)等领域,相关内容简介如下:

图三 马宇飞研究员

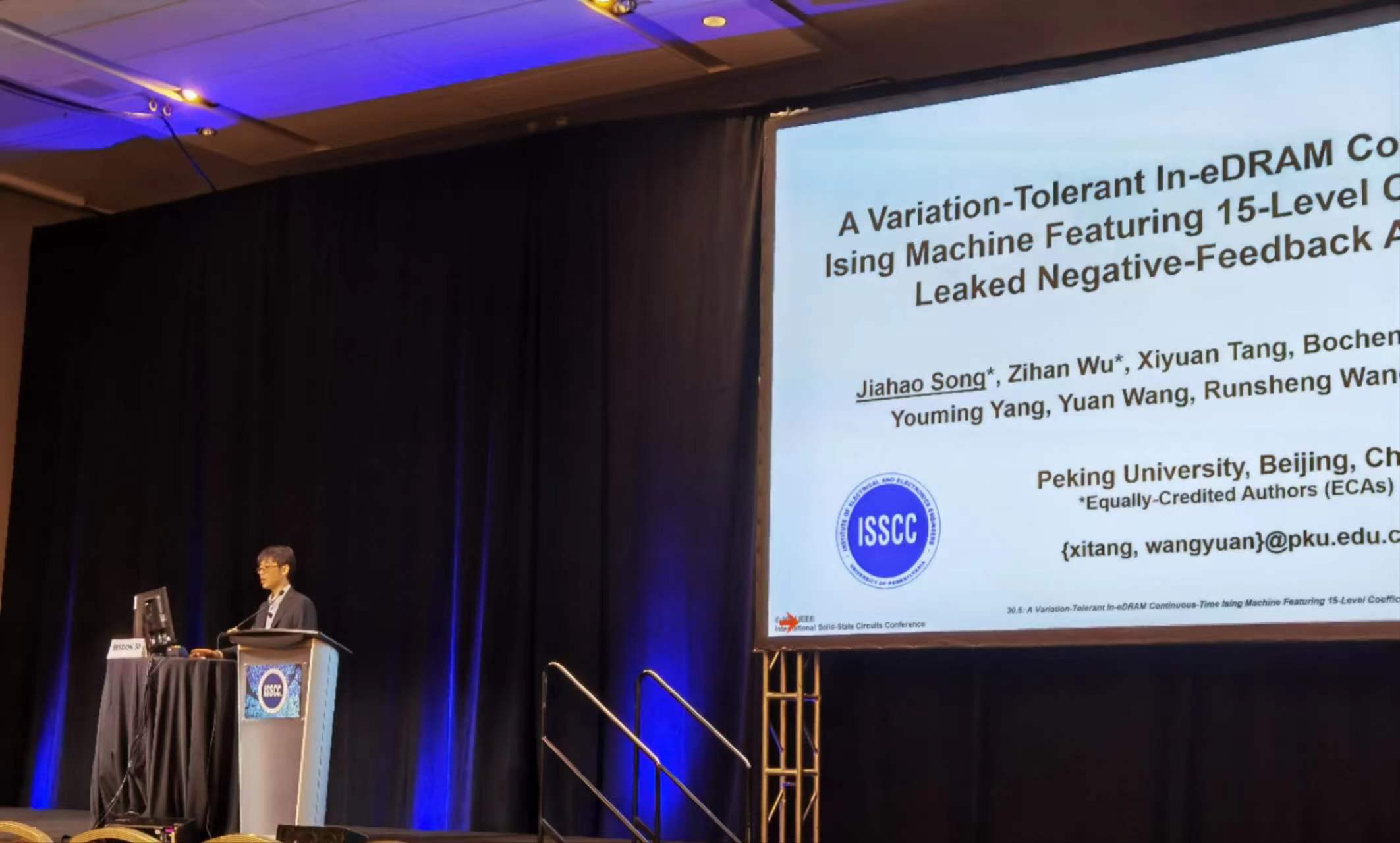

图四 博士后宋嘉豪

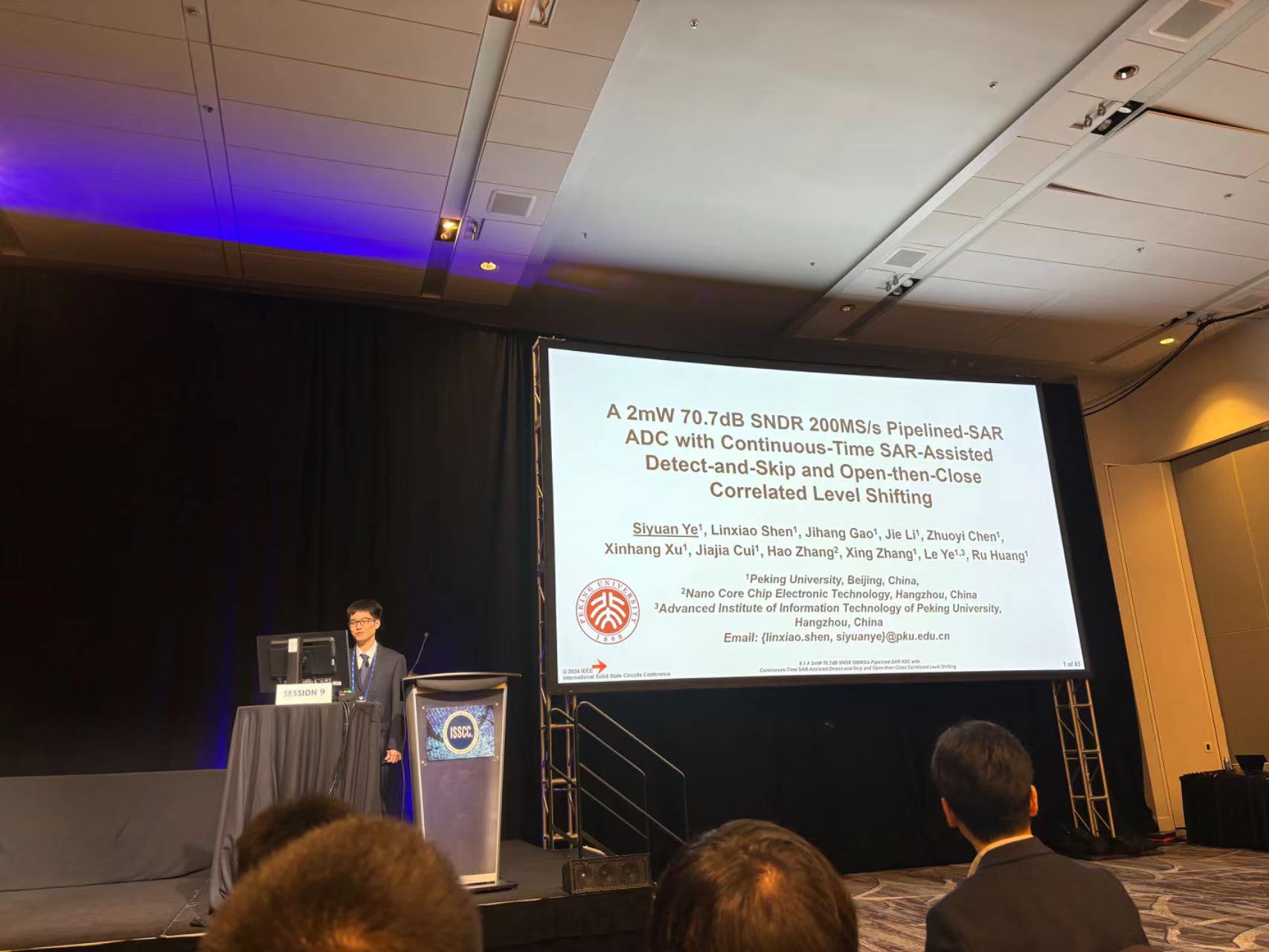

图五 博士生叶思源

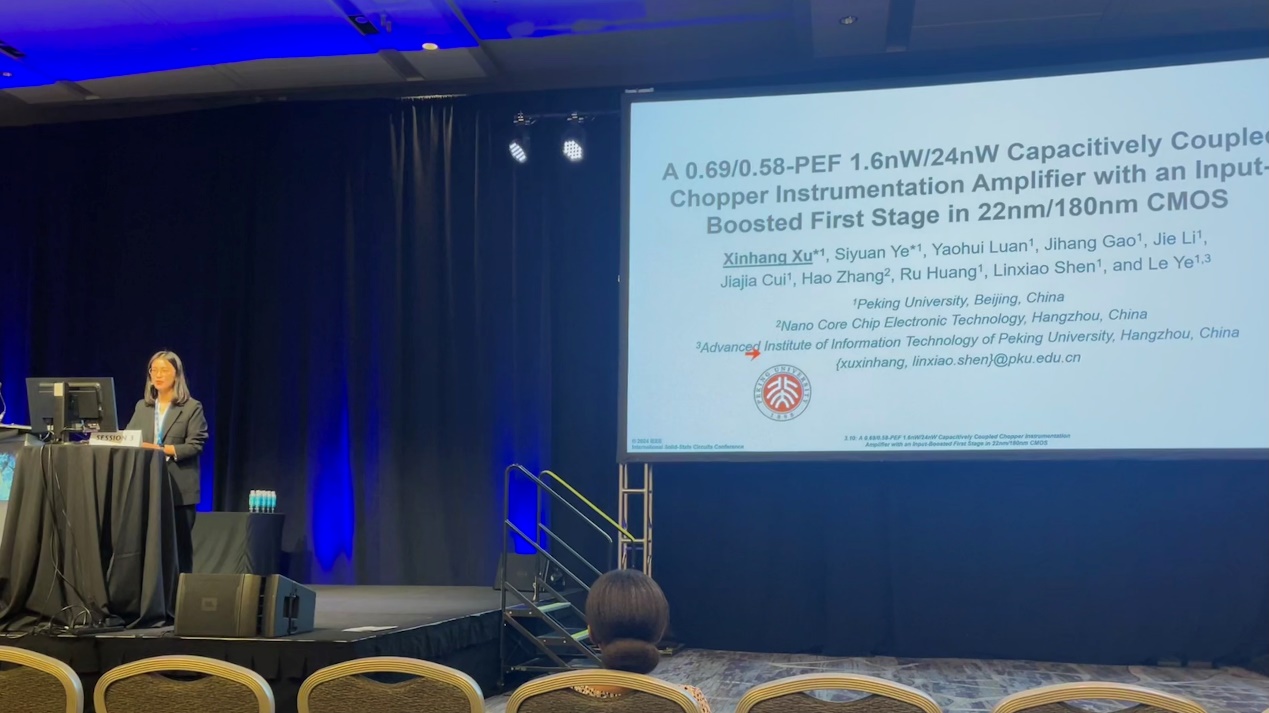

图六 博士生许欣航

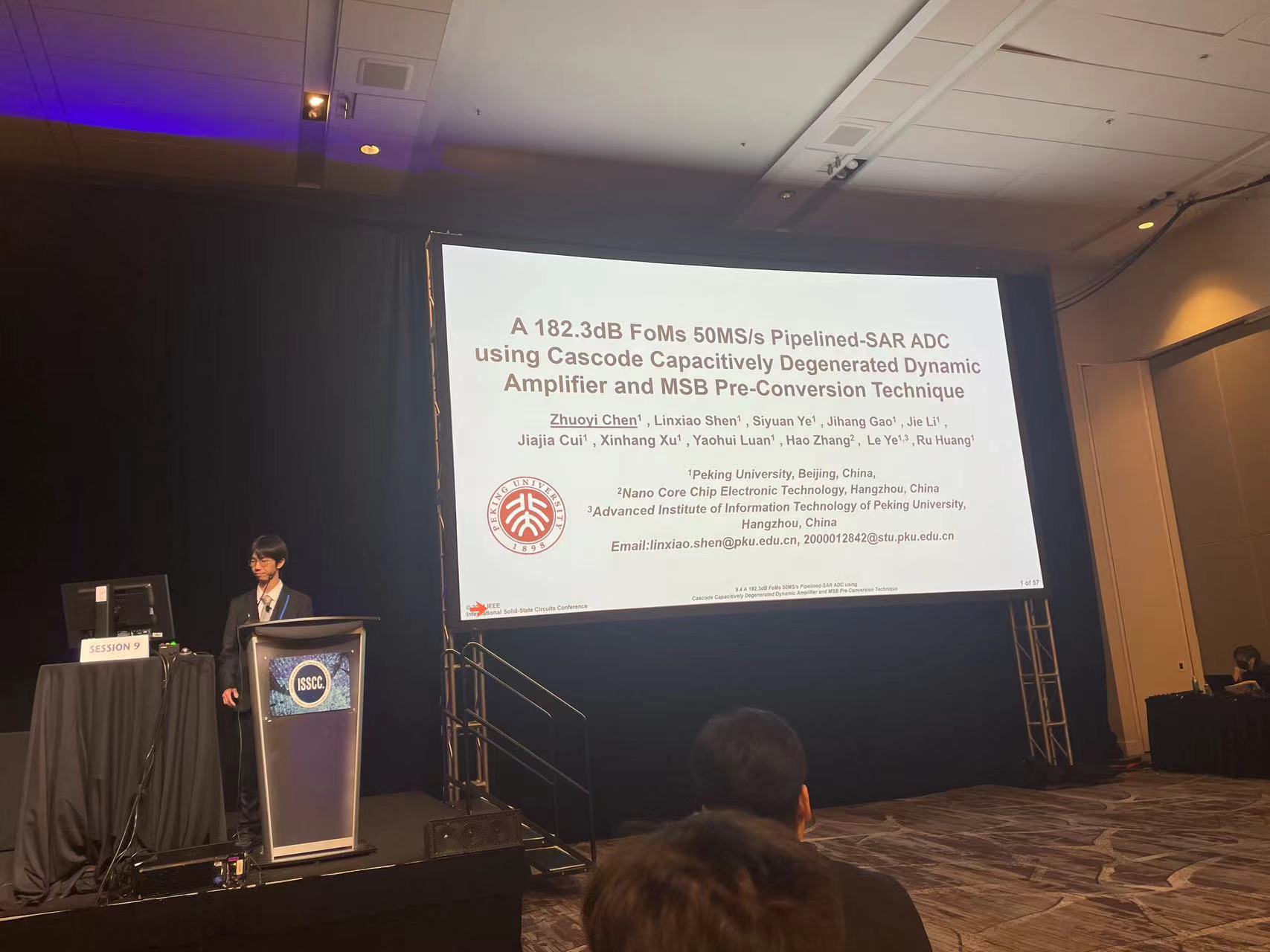

图七本科生陈卓毅

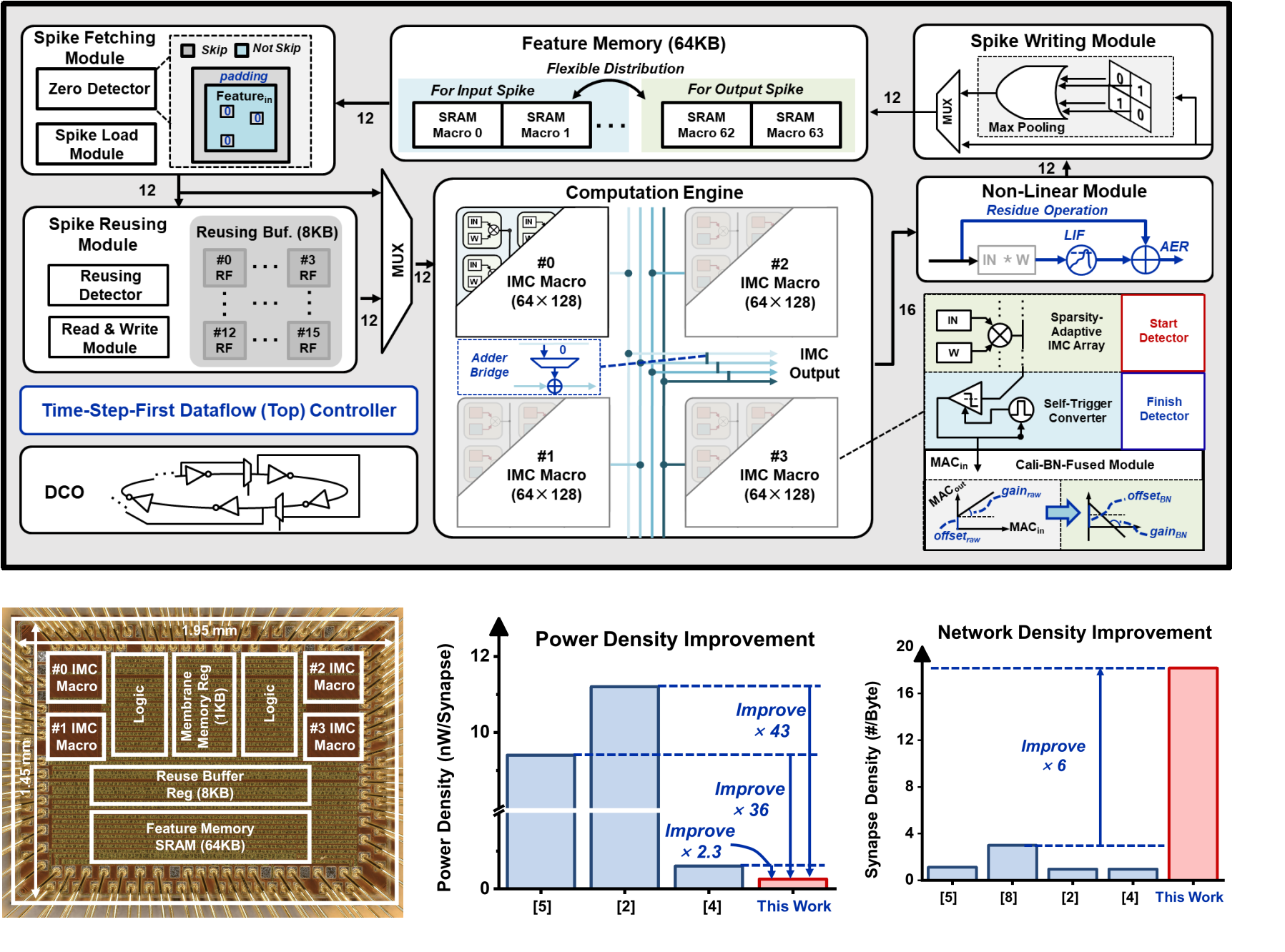

(一)基于SRAM存算一体的高能效类脑芯片

面向边缘AI的应用场景,均使用稀疏脉冲作为信息介质的动态视觉传感器和脉冲神经网络推理引擎提供了可靠的高能效解决方案。课题组为了在有限的存储资源和功耗下,芯片能够集成更多的突触连接数量以提升芯片的推理能力,针对传统脉冲神经网络芯片中存在的突触权重,膜电位等数据类型在多时间步上数据搬运的问题,创新性地融合了时间步优先的数据流和存算一体阵列技术,使得权重在整个时间窗口内缓存于存算一体的子阵列中,最小化数据的片内外搬运次数。

北京大学黄如院士-叶乐教授团队,提出了时间步数据流和SRAM存算一体融合架构,利用存算一体阵列以避免突触权重在多时间步上的数据搬运;提出了无时钟自适应稀疏性存算一体电路技术,依据脉冲神经网络输入稀疏性,存算一体阵列实现动态调整计算延迟和计算功耗,并且无需任何全局时钟,通过异步握手信号控制以适应事件触发特性;此外,还使用了高细粒度的脉冲触发和时钟门控电路设计方法,最小化降低时钟树带来的“暗硅”消耗。

基于以上创新技术,研制了基于存算一体的领域专用脉冲神经网络芯片,在22nm工艺下,该芯片可实现每突触结构消耗0.26nW的功耗密度,以及18 Synapse/bit的存储密度,相比国际最好水平分别优化6倍和2.3倍。该芯片具备高能效,高网络密度,低功耗密度等优势,可应用于边缘端AI,如图像分类,目标识别等应用场景。

该工作以《基于时间步优先数据流和稀疏自适应存内计算技术的0.26nW/突触脉冲神经网络处理单元》(A 22nm 0.26nW/Synapse Spike-Driven Spiking Neural Network Processing Unit Using Time-Step-First Dataflow and Sparsity-Adaptive In-Memory Computing)为题,发表于今年ISSCC的领域专用计算和数字加速器(Session 30 Domain-Specific Computing and Digital Accelerators)分会场,该文章第一作者为北京大学博士生刘影和马宇飞研究员,并由马宇飞研究员进行宣讲,通讯作者为北京大学叶乐教授和王志轩。该工作由北京大学集成电路学院、微纳核芯电子科技有限公司和北京信息科技大学,以及“国家自然科学基金”、“浙江省重点研发计划”、“111计划”、集成电路高精尖创新中心等项目提供支持。

(a)时间步优先数据流的存算一体脉冲神经网络芯片架构;(b)芯片显微照片; (c)性能对比优势;

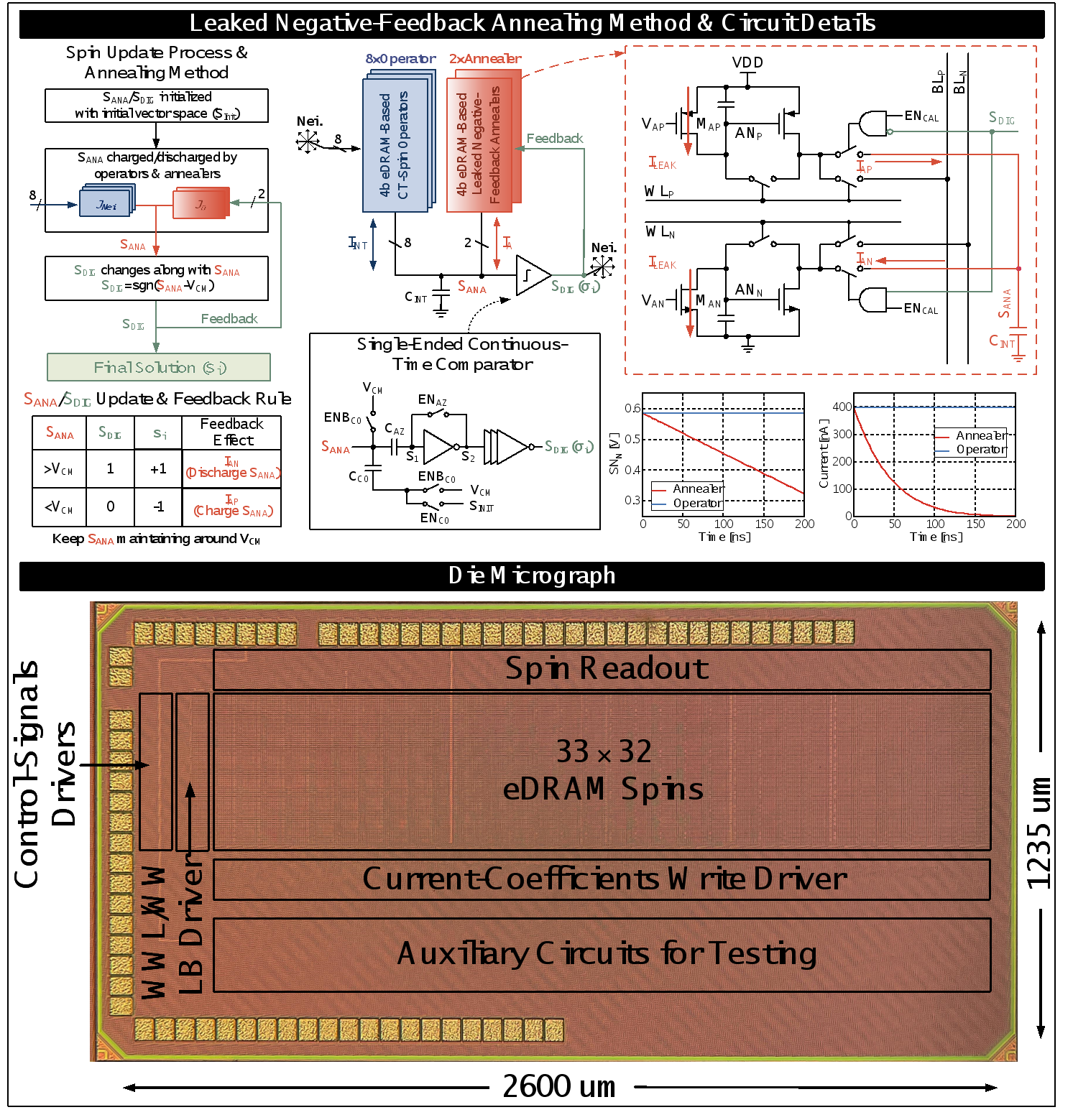

(二)连续时间存内伊辛机芯片

该工作面向组合优化问题求解,针对不断提升的计算速度、系数精度、与求解质量需求,设计并实现了一款具有多值互联系数,嵌入退火功能的连续时间存内伊辛机芯片,突破了传统连续时间伊辛机的系数精度与求解质量瓶颈。

针对以上瓶颈,北京大学王源教授-唐希源研究员团队提出了基于嵌入式动态随机存储器的存内伊辛机:该技术创新性地使用电流编程动态随机存储器来进行存内连续时间自旋节点更新。在相互作用系数写入时,编程电流产生自校准的权重电压,实现多值模拟相互作用系数的高精度编程。与此同时,针对连续时间伊辛机的求解质量问题,课题组采用负反馈来帮助系统跳出局部最优解,并利用动态随机存储器中的漏电来逐渐降低负反馈强度,模拟退火过程,从而达到更高的求解质量。

基于以上创新技术,课题组研制了基于动态随机存储器的连续时间存内伊辛机芯片。在65nm工艺下,该芯片可实现15值的相互作用系数,小于20.7ns的最快求解速度,0.33nJ的求解能量,以及848um2/Spin的面积效率,并在工艺、电压、温度偏移下均有高稳定性。该芯片具备高求解速度、高系数精度、和高求解质量等优势,在现实生活中时间关键的组合优化问题求解中极具应用前景。

该工作以《A Variation-Tolerant In-eDRAM Continuous-Time IsingMachine Featuring 15-Level Coefficients and LeakedNegative-Feedback Annealing》为题,发表于今年ISSCC的领域专用计算和数字加速器(Session 30 Domain-Specific Computing and Digital Accelerators)分会场。北京大学集成电路学院博士后宋嘉豪和博士生吴子涵共同一作,通讯作者为唐希源研究员和王源教授。文章由宋嘉豪博士进行宣讲。该工作由北京大学集成电路学院,以及“国家自然科学基金”、“国家自然科学基金联合基金”、“111计划”、集成电路高精尖创新中心等项目提供支持。

(a)自旋节点原理图与更新示意图以及创新退火技术;(b)芯片显微图

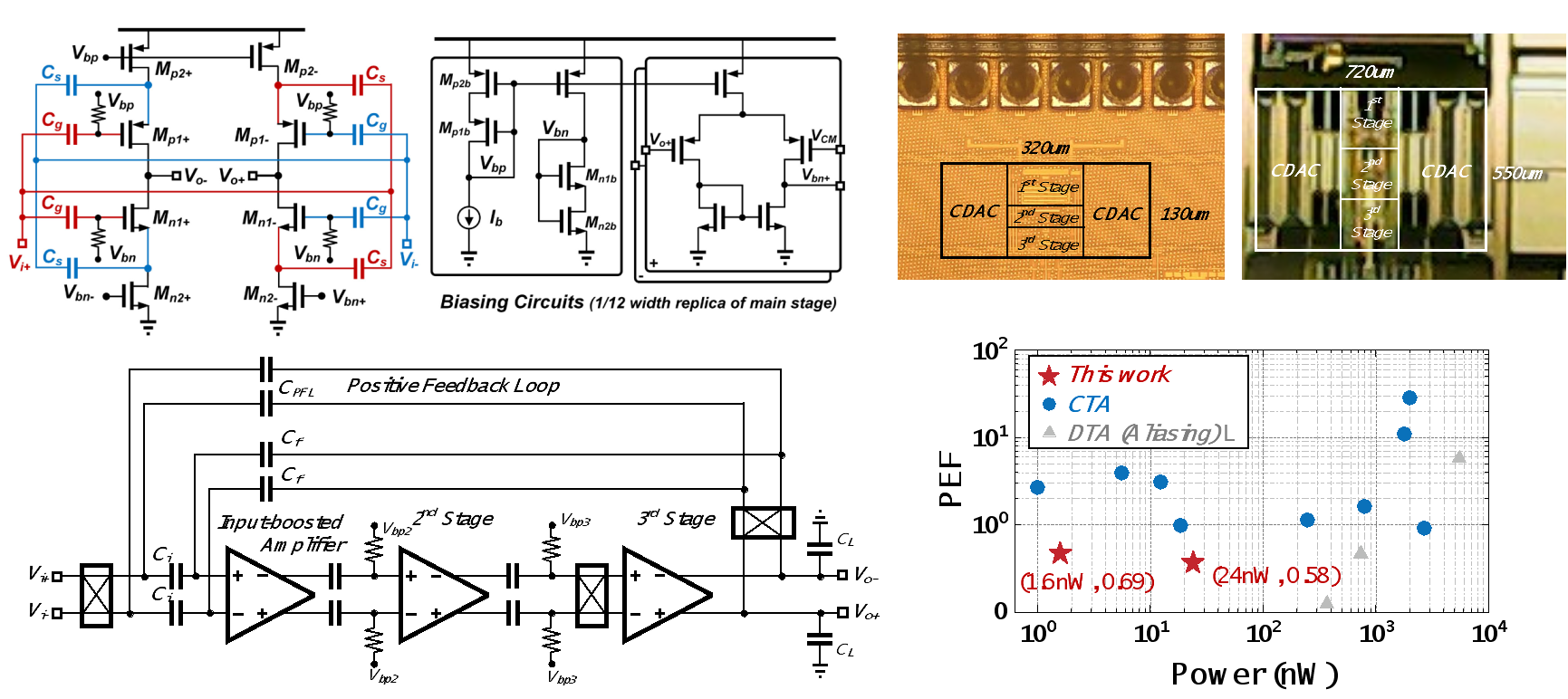

(三)高能效模拟前端放大器芯片

该工作面向物联网传感器芯片应用,针对不断提升的高能效模拟前端放大器需求,设计并实现了一款超高能效、超低功耗的电容耦合型斩波仪表放大器,突破了传统放大器中功耗与噪声之间折中关系的性能瓶颈,跨工艺验证得到其综合性能达到国际领先水准。

针对以上瓶颈,北京大学黄如院士-叶乐教授团队,提出了基于输入倍增技术的高能效放大器:该技术创新性地提出了输入信号倍增技术,将输入耦合到输入对管的栅极与源极从而提升其等效增益,在相同的功耗下实现了更低的噪声水平。与此同时,针对超低功耗应用中的漏电问题,采用漏电补偿技术解决了寄生阱二极管与开关衬底漏电导致的直流偏置偏移问题。

基于上述创新理念与技术,课题组在180nm CMOS和22nmCMOS下分别研制出了一款高能效放大器。在180nm工艺下该结构以24nW的功耗实现了1.6kHz带宽内5uV的积分噪声;在22nm工艺下以1.6nW的功耗实现了230Hz带宽内8uV的积分噪声;在综合评估放大器能效的指标(Power efficiency factor, PEF)下,分别达到了0.58和0.69的指标,是目前能效最优的连续时间模拟前端放大器。该放大器在不同温度与电压下进行了验证,保证了其在复杂工作环境下的稳定性。该电路可广泛应用于面向传感应用的物联网芯片中,作为其中模拟信号链最前端的模块。

该工作以《A 0.69/0.58-PEF 1.6nW/24nW Capacitively Coupled Chopper Instrumentation Amplifier with an Input-Boosted First Stage in 22nm/180nm CMOS》为题,发表于今年ISSCC的模拟技术分会场(Session 3 AnalogTechniques)。文章第一作者北京大学集成电路学院博士生许欣航进行宣讲,北京大学集成电路学院博士生叶思源为共同一作,文章的通讯作者为沈林晓研究员和叶乐教授。该工作由北京大学集成电路学院、微纳核芯电子科技有限公司和浙江省北大信息技术高等研究院,以及“国家重点研发计划”、“国家自然科学基金”、“北京市科技新星计划”、“111计划”、集成电路高精尖创新中心等项目项目提供支持。

(a) 基于输入倍增技术的电容耦合型斩波仪表放大器;(b) 芯片显微照片;(c) 性能对比图

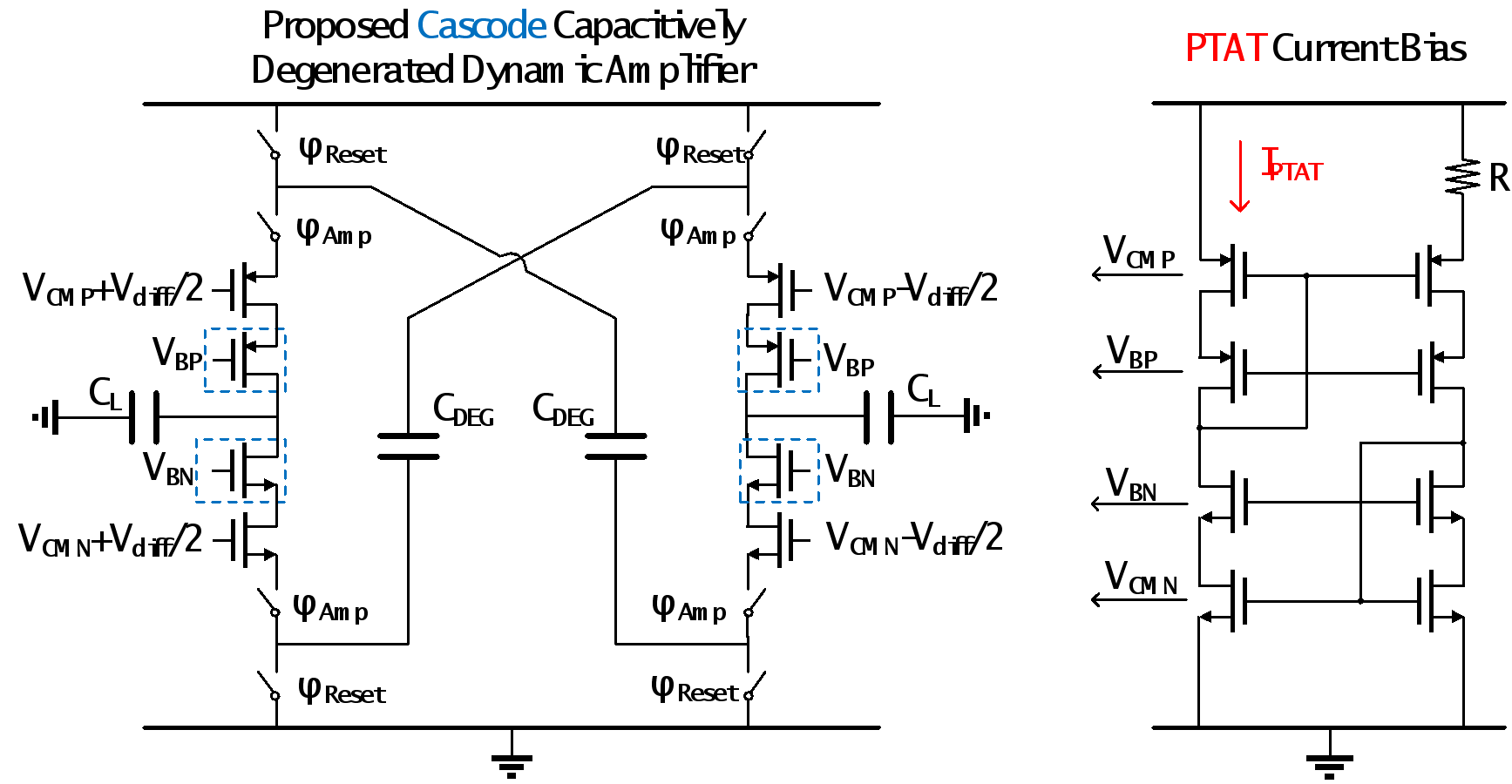

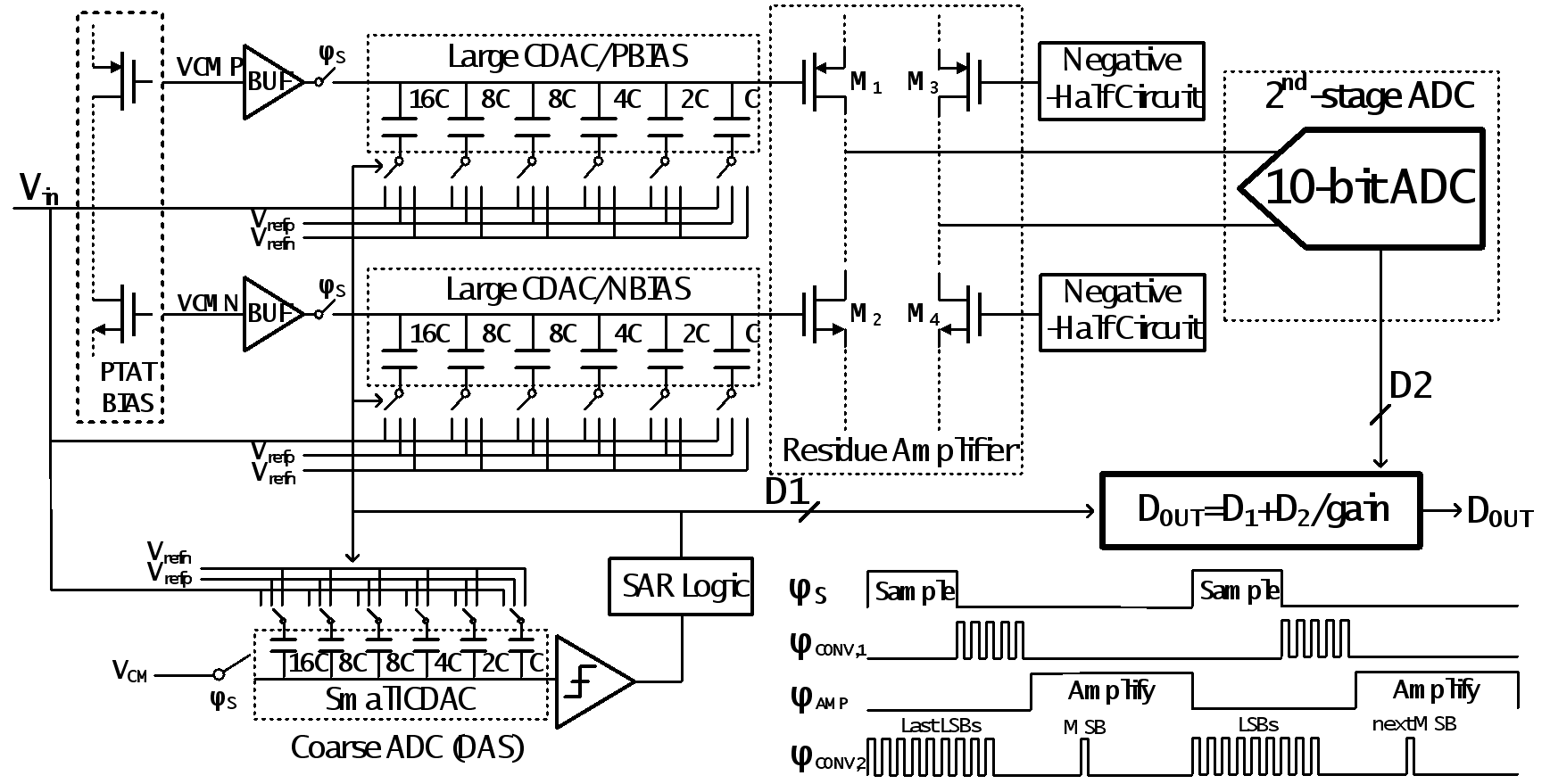

(四)高能效模数转换器芯片

该工作面向通信、医学成像等需求,针对不断提升的高能效模数转换器的需求,提出了一个高性能,低功耗的动态放大器,解决了传统动态放大器线性度差、增益低、输出摆幅小等问题,并将其应用于模数转换器中,实现了极高能效的流水线-逐次逼近型模数转换器芯片。

针对以上问题,北京大学黄如院士-叶乐教授团队,首次提出了共源共栅的容性源极负反馈的动态放大器和最高位提前转换技术:其中共源共栅的容性源极负反馈的动态放大器改良了之前的技术,具有高线性度和高增益的特点,同时采用了温度补偿的电流偏置方案提升了PVT涨落下的性能鲁棒性。而另一方面,最高位提前转换技术在余量放大的过程中进行了第二级最高位的转换,这不仅进一步提高了动态放大器的输出摆幅,同时让第二级的最高位切换更快稳定。值得一提的是,这个技术获得的这些好处并不需要引入额外的硬件开销。利用以上技术,本工作提出了一个高能效、高增益、高线性度、高输出摆幅且PVT鲁棒的动态放大器,并实现了一个高能效的流水线-逐次逼近型模数转换器芯片。

基于上述架构和电路层面的创新,课题组研制了一款基于22nmCMOS工艺的高能效流水线-逐次逼近型模数转换器,该电路在奈奎斯特输入下达到了73.9dB的SNDR,仅消耗0.36mW。这达到了目前在相同或更高采样率的模数转换器中能效的世界纪录(FoMs=182.3dB)。

该工作以《基于容性源极负反馈的共源共栅动态放大器和最高位提前转换技术的FoMs=182.3dB的流水线-逐次逼近型模数转换器芯片》(A 182.3dB FoMs 50MS/s Pipelined-SAR ADC using Cascode Capacitively Degenerated Dynamic Amplifier and MSB Pre-Conversion Technique)为题,发表于今年ISSCC的逐次逼近和噪声整形模数转换器领域(Session9 SAR and Noise Shaping ADCs)分会场,由文章第一作者北京大学集成电路学院本科生陈卓毅进行宣讲,文章的通讯作者是沈林晓研究员和叶乐教授。该工作由北京大学集成电路学院、微纳核芯电子科技有限公司和浙江省北大信息技术高等研究院,以及“国家重点研发计划”、“国家自然科学基金”、“北京市科技新星计划”、“111计划”、集成电路高精尖创新中心等项目提供支持。

(a)动态放大器结构;(b)高速转换器架构

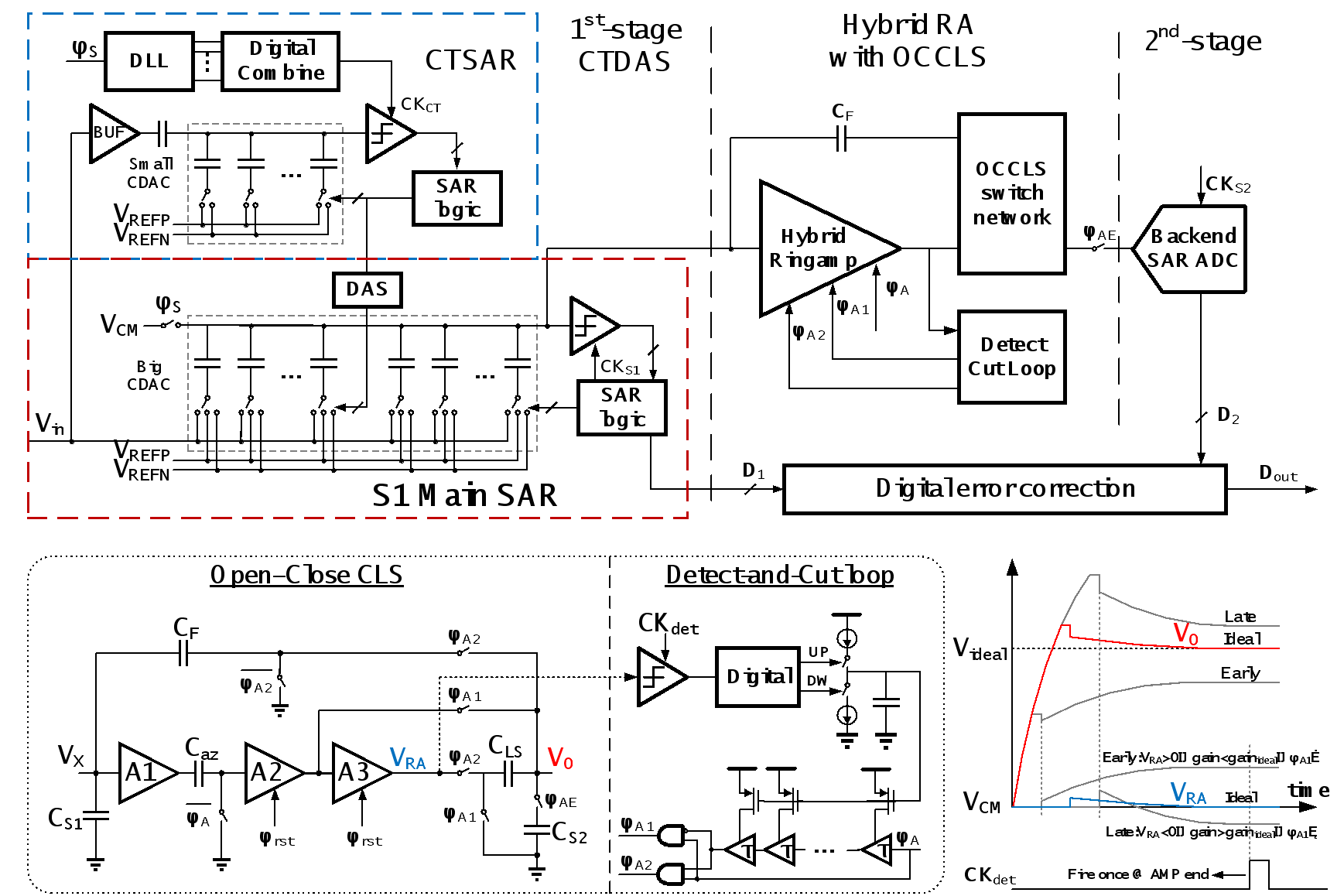

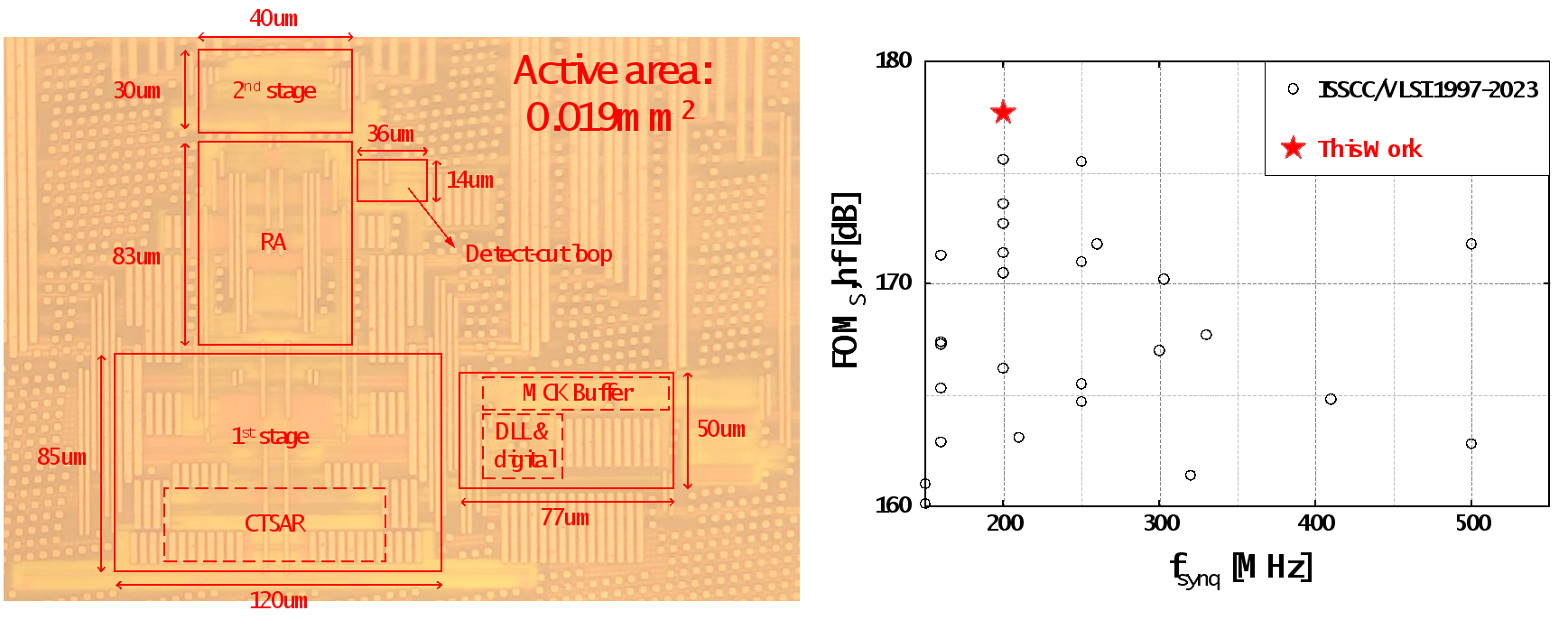

(五)高速高精度模数转换器芯片

该工作面向宽带通信系统应用,针对不断提升的高速高精度模数转换器的要求,提出并实现了一款高速,高精度,高能效的流水线-逐次逼近型模数转换器,突破了传统流水线-逐次逼近型模数转换器的架构中转换级和级间放大器两大速度和能效的瓶颈。

针对以上瓶颈,北京大学黄如院士-叶乐教授团队,针对转换级和级间放大器两个方面提出解决方案。转换级方面,本工作提出了基于连续时间逐次逼近型模数转换器的采样转换并行技术,创新性地将模数转化器的采样过程与高位量化过程并行起来,从而在保持高能效的同时显著缩短转换级的采样转换时间,提升了整体的速率;级间放大器方面,本工作首次提出了基于先开环后闭环的相关电平抬升技术,利用开环放大显著提升余量放大的速率,同时采用了自检测切断环路用于实现工艺电压温度鲁棒的高增益。此外,本工作还提出了混合静态-动态环形放大器的电路架构,显著提高了级间放大器的噪声和能效性能。在提高采样转换速率的同时,本工作实现了高速高精度模数转换器的能量效率世界纪录,相较现有工作将能效提升将近一倍。

基于上述架构和电路层面的创新,课题组研制了一款基于22nm CMOS工艺的高速高精度高能效的模数转换器芯片。在22nm工艺下,该芯片在200MS/s的采样率下实现了70.7dB SNDR的精度和2.0mW的功耗,在所有相同或更高采样率的模数转换器中达到了能量效率的世界纪录(177.7dB FoMs),相较前人的工作将能效提升了将近一倍。该电路具有高速,高精度,高能效等特点,可广泛应用于宽带通信和射频前端,高保真音视频信号接口处理,工业控制测量等应用中。

该工作以《基于连续时间逐次逼近型模数转换器的检测跳过技术和先开环后闭环的相关电平抬升技术的2mW, 70.7dB SNDR, 200Msps的流水线逐次逼近型模数转换器芯片》(A 2mW 70.7dB SNDR 200MS/s Pipelined-SAR ADC with Continuous-Time SAR-Assisted Detect-and-Skip and Open-then-Close Correlated Level Shifting)为题,作为模数转换器方向的亮点论文(highlight),发表于今年ISSCC的噪声整形和逐次逼近型模数转换器领域(Session9 Noise Shaping and SAR ADC)分会场,由文章第一作者北京大学集成电路学院博士生叶思源进行宣讲,文章的通讯作者是沈林晓研究员和叶乐教授。该工作由北京大学集成电路学院、微纳核芯电子科技有限公司和浙江省北大信息技术高等研究院,以及“国家重点研发计划”项目、“国家自然科学基金”、“北京市科技新星计划”、“111计划”、集成电路高精尖创新中心等项目提供支持。

(a)流水线-逐次逼近型模数转换器架构图和创新技术;(b)芯片显微图和性能对比图

ISSCC背景介绍

ISSCC(国际固态电路年度会议)于每年2月中旬在美国旧金山举行,是全球芯片设计领域最具影响力、最权威的学术盛会。被誉为“集成电路设计领域的奥林匹克大会”,该会议吸引了来自世界各地的工程师、科学家和产业专家,共同探讨集成电路技术的最新进展和未来趋势。每年约有200项芯片实测成果入选,其中约四成来自于国际芯片巨头公司,如英特尔、三星、台积电、AMD、英伟达、高通、博通、ADI、TI、联发科等。其余六成左右的芯片成果则来自于高校和科研院所。历年入选的成果代表着当年度全球领先水平,展现出芯片技术和产业的发展趋势。多项“芯片领域里程碑式发明”首次在ISSCC上披露,例如世界上第一个集成模拟放大器芯片(1968年)、第一个8位微处理器芯片(1974年)和32位微处理器芯片(1981年)、第一个1Gb内存DRAM芯片(1995年)、第一个多核处理器芯片(2005年)等。这一盛会不仅是学术交流的平台,更是推动芯片技术创新的重要驱动力。