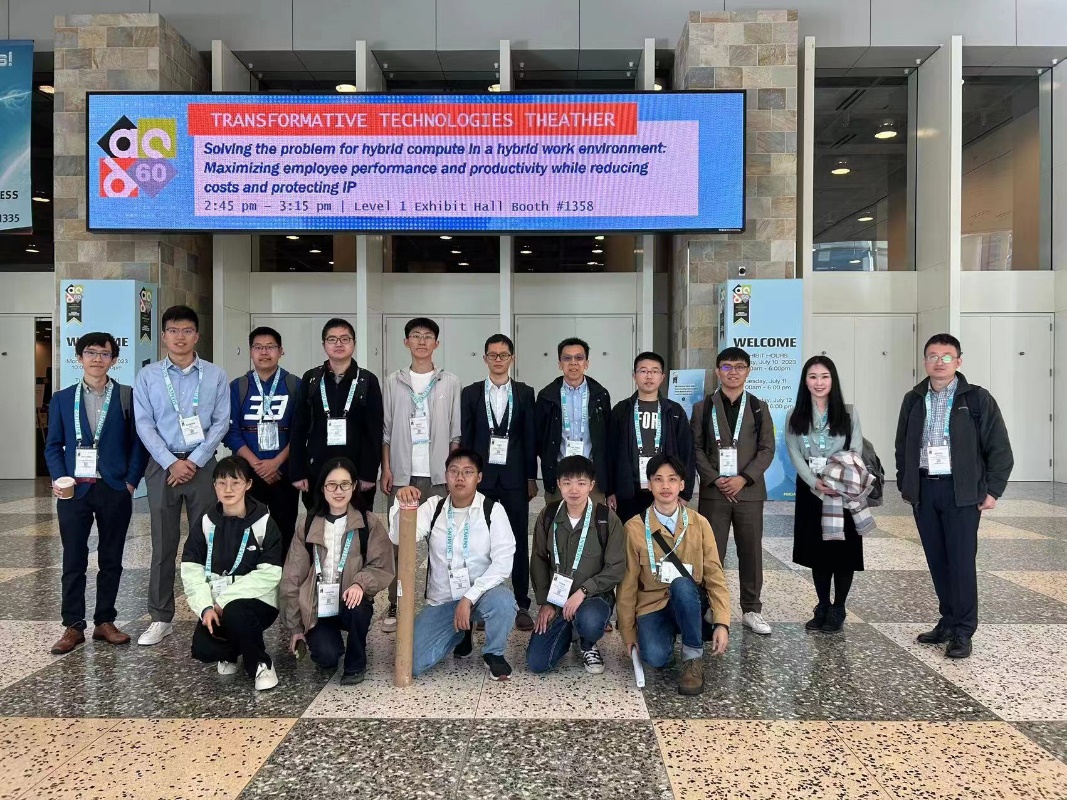

7月9日至13日,第60届设计自动化会议(DAC 2023)在美国旧金山召开。在本次大会中,来自电子设计自动化(EDA)与集成电路领域的高校、公司及研究机构群英荟萃,分享了EDA技术的最新发展和广泛应用,讨论了本领域进一步发展的前景和方向。北京大学也积极参与了本次大会的组织,李萌老师是DAC 2023 System Design Contest(SDC)的组织者之一,北京大学EDA研究院也是该竞赛的主要支持单位;此外,多位老师包括李萌、马宇飞、王宗巍、燕博南等也担任了DAC的程序委员会(TPC)成员。集成电路学院的十余位老师和同学现场参加了本次大会,进行了汇报与交流。

大会主旨报告

李萌老师主持SDC竞赛

学院部分参会老师与学生合影

在本次大会上,北京大学集成电路学院/集成电路高精尖创新中心共有9篇论文入选,研究成果覆盖了芯片设计、综合技术、体系架构、仿真验证、异构计算、设计自动化、软硬件协同等领域。相关介绍如下:

一、存内计算神经网络加速器的流水线优化

基于非易失性存储器的存内计算神经网络加速器具有权重预存储的特点,通过流水线设计提高存内计算宏单元的时间利用率是提高神经网络加速器系统吞吐量的有效解决方案,然而,现有的流水线架构设计很少从整个系统的角度来关注流水线优化,特别是忽略了缓冲区访问的影响。黄鹏助理教授团队在综合考虑了计算和存储延迟后,分别从算子级、宏单元级和系统级优化了权重映射和流水线方案。实验结果表明提出的优化方案在主流卷积神经网络识别ImageNet数据集的任务上实现了超过3倍的系统吞吐量提升。该工作以《A convolutional neural network accelerator design with weight mapping and pipeline optimization》为题发表(博士生韩丽霞为第一作者,通讯作者是黄鹏助理教授)

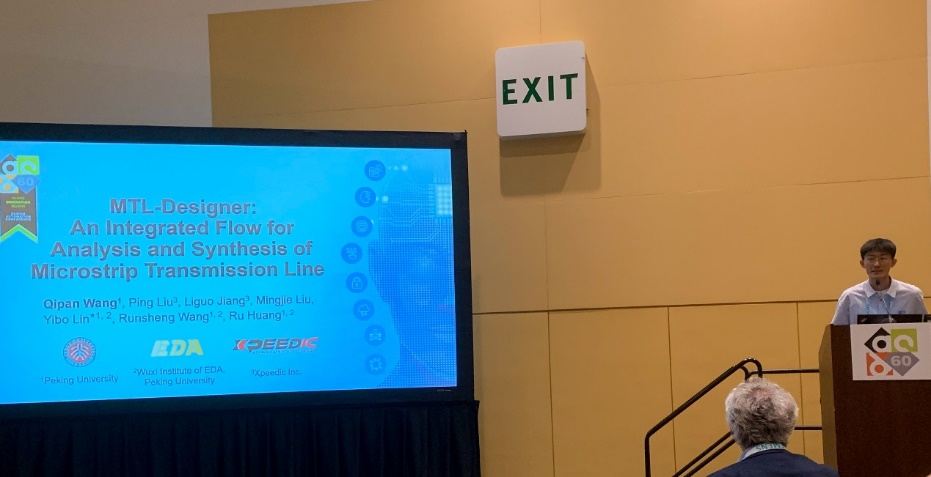

二、微带线快速综合算法

微带线是一种可以传输微波信号的常见传输线,通过改变其电学和几何 参数,微带线可以实现不同的传输特性,广泛用于现代微波集成电路和高速数字 PCB 设计。现有的微带线分析和综合方法在设计精度、设计规范 和设计结构等方面存在不足,难以有效支持微波集成电路的自动化设计。针对以上问题,林亦波研究员-王润声教授团队与国内的EDA公司芯和合作,提出了一种基于深度学习的微带线自动化分析设计方法。该方法结合了深度生成模型和基于神经网络的替代模型,可以在给定设计规范和设计约束的情况下,设计大量可行的微带线电学和几何参数。经过严格模拟工具TmlExpert验证,该方法可以准确高效地预测微带线特征阻抗,并在短时间内提供多组可行的设计参数,特征阻抗精度>99.6%。该工作以《MTL-Designer: An Integrated Flow for Analysis and Synthesis of Microstrip Transmission Line》为题发表(博士生王启盼为第一作者,通讯作者是林亦波研究员)。

三、随机计算非线性加法器

随机计算是一种基于概率的计算范式,其通过使用比特流代替传统二进制编码进行计算,有望实现高面积效率的算术电路和很好的容错性,非常适合用于边缘计算的神经网络加速。近年来,随机计算用于网络加速的相关研究受到广泛关注,研究者们在一些小模型的加速器上达到了非常高的能效。然而之前的工作中,占据90%以上面积的非线性加法器在支持大模型时仍然面临着效率和灵活性瓶颈。因此,李萌研究员-王润声教授团队提出了基于截断-量化的近似压缩技术:针对现有的一种使用排序网络和选择性互联系统组成的非线性加法器设计,该技术利用排序网络的递归构造特性,在对子网络的输出进行截断和量化,从而大大减少后续电路的成本,并且将各种不同的压缩配置量化为四个参数而得到了一个近似电路的设计空间;进一步,提出了一种时间-空间展开的灵活设计模式,可以将此前完全并行的大电路拆分为多周期复用的小模块,从而大大提升了非线性加法器在处理模型中不同规模累加运算的灵活性。基于上述创新技术,课题组对提出的近似随机计算非线性加法器设计与现有随机计算非线性加法器在CIFAR10数据上的ResNet18网络进行了比较。在最大的卷积层任务上,本研究提出的空间展开近似设计和时间-空间展开近似设计分别比原始设计提升了2.8倍和4.1倍的硬件效率;由于时间-空间展开带来的显著灵活性提升,在更小的卷积层中,时间-空间展开近似设计相较于原始设计提升了4.1倍至23.3倍的硬件效率,平均而言,提升了8.47倍非线性加法器部分的硬件效率。从另一方面而言,该优化使得整个数据通路上的电路面积减少了2.2倍。课题组的此项工作成功实现了更加有效和灵活的随机计算非线性加法器。改工作以《Efficient Non-Linear Adder for Stochastic Computing with Approximate Spatial-Temporal Sorting Network》为题发表(博士生胡逸轩为第一作者,李萌研究员为通讯作者)。

四、张量聚合算子的设计空间探索框架

张量聚合算子被广泛用于推荐系统、图神经网络等应用的特征提取操作中。这一算子有着访存密集的特点,因此基于DIMM的近存计算技术被广泛应用于这一算子的加速。然而,在不同场景下,张量聚合算子对近存计算架构设计有着不同的偏好,不恰当地选取架构设计配置无法充分发挥近存计算架构的性能。针对这一问题,孙广宇副教授团队提出了一套高效的设计空间探索框架。在给定应用场景和硬件参数的情况下,该框架可以生成并探索更大范围的架构设计,并给出最优的架构配置。为了避免耗时的仿真,我们进一步提出了一个性能评估模型,用于快速评估设计空间中的各种架构配置。该工作以《NMExplorer: An Efficient Exploration Framework for DIMM-based Near-Memory Tensor Reduction》为题发表(博士生李聪为第一作者,孙广宇副教授为通讯作者)。

五、用于大型图MPL分解问题的可扩展低秩SDP求解器

多重图形光刻(MPL)已被广泛应用于先进技术节点,以增强光刻分辨率。大多数现有的MPL分解研究在构建分解图后都遵循两步骤的过程:首先将图分解成小的子图,然后在子图上应用分解算法。这些分解算法基于整数线性规划(ILP)、半正定规划(SDP)、精确覆盖(EC)或其他图启发式算法。在这些方法中,ILP可以以指数复杂度提供精确解,而SDP和EC则可以在可接受的运行时间内提供高质量的近似解。然而,这些方法通常假设简化步骤后的子图较小,当设计复杂性增加时,子图的大小也会增加。林亦波研究员团队观察到,通过SDP求解,2.2%的大图占据了94.5%的运行时间,而87.9%的小图仅占总运行时间的0.1%。因此,迫切需要新的分解算法来提高处理大型设计的效率。为了实现高效且高质量的分解,团队提出了一种用于大型图MPL分解问题的可扩展低秩SDP求解器LRSDP,采用基于分解的增广拉格朗日方法(ALM)来解决MPL的大规模SDP问题。这种方法利用问题结构,通过将搜索空间限制在平滑流形(单位球)上,采用Barzilai–Borwein步长的黎曼梯度下降方法(RGBB)来高效地搜索最优解。结果表明,与最先进的算法包括ILP、EC、SDP相比,LRSDP方法在ISPD2019测试集上可以实现186倍、25倍和12倍的加速,并且相比原本的SDP求解器具有更好的分解质量;LRSDP甚至可以扩展到其他算法无法解决的更大规模情形。该工作以《LRSDP: Low-Rank SDP for Triple Patterning Lithography Layout Decomposition》为题发表(博士生陈一帆为共同第一作者,林亦波研究员为通讯作者)。

六、GPU加速逻辑仿真方法

带延迟标注的门级逻辑仿真在芯片设计流程中具有重要地位,然而它极为耗时。针对百万门级设计的逻辑仿真通常需要数小时乃至数天才能完成,这拖慢了整个芯片设计迭代的周期。这类逻辑仿真运行缓慢的根本原因是它难以进行快速、准确的并行计算,而这是由于信号传播因果关系的建模具有内在的复杂性。针对这一难题,林亦波研究员-王润声教授团队提出了基于稳定时间机制的带延迟逻辑后仿加速技术。这一技术精确计算了末次信号翻转事件的持续时间(即稳定时间),利用状态压缩动态规划方法,针对任意种类的时序逻辑门预处理输出和输入之间的敏感性依赖关系,建立逻辑单元库的扩展状态表。在扩展状态表的基础上,门级逻辑仿真按电路拓扑顺序并行传播信号翻转事件,同时推理出下一逻辑层级的最长稳定时间。利用这一算法,此工作在学术界首次实现了通用、无需图分割的并行门级逻辑仿真算法,并实现了CPU/GPU异构并行计算平台上的高效仿真,相比商业工具实现了平均7.8倍的加速。该工作以《General-Purpose Gate-Level Simulation with Partition-Agnostic Parallelism》为题发表(博士生郭资政为第一作者,林亦波研究员为通讯作者)。

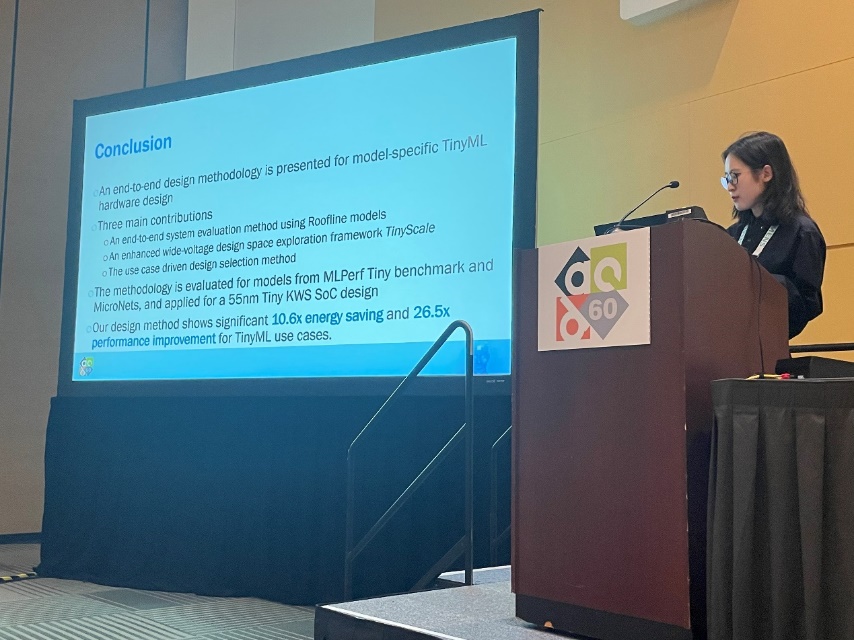

七、TinyML异构硬件的端到端设计方法

在智能边缘芯片的异构设计复杂度不断提高、算力需求不断上升、硬件资源持续受限等现状下,针对智能边缘芯片面临的来自架构建模、功耗优化、设计方法等多方面的设计挑战和研究需求,叶乐副教授-黄如院士团队提出了一种面向资源受限的TinyML异构硬件的端到端设计方法。该工作主要包括三个贡献。首先,提出了使用Roofline模型的端到端系统评估方法,支持不同算力人工智能加速模块以及通用计算模块的系统性能评估,实现覆盖常见低功耗异构架构的芯片模型选择;其次,在满足边缘应用的实时性要求下,提出在包括近阈值在内的广阔设计空间中探索最优最小能耗点探索方法,通过迭代优化算法评估和优化架构,实现智能边缘芯片的异构架构功耗优化;最后,提出端到端应用驱动的设计空间探索方法,针对特定领域应用模型或者同一类应用模型进行系统性设计,实现特定应用的最优异构架构设计。该设计方法在TSMC 22nm和55nm工艺上进行了评估,与基础架构相比,使用该设计方法在端到端任务中实现了10.6倍的能效和26.5倍的EDP性能提升。此外,该设计方法也应用于实际的关键词识别SoC芯片实现,通过在所有目标用例中探索架构和工作电压条件,该设计可节省13倍的能耗。该工作以《A Model-Specific End-to-End Design Methodology for Resource-Constrained TinyML Hardware》为题发表(博士生董彦池为第一作者,贾天宇研究员和叶乐副教授为通讯作者)。

八、面向异构SoC的调度算法设计

多模型、多模态推理部署广泛应用于人工智能应用,与计算异构性相对应的是硬件架构的异构性,在同一系统中往往存在架构不同、功能不同的计算单元。为了充分发挥硬件计算性能,需要将多模型进行拆解并将不同的算子映射在不同的计算单元中。然而,同一系统中的计算单元算力差距大,算力强的计算单元可以同时处理多个算子,而算力弱的单元需要将算子拆分后分块计算,因此对不同单元使用相同的调度策略往往会造成算力的使用不充分、不均衡。此外,计算单元之间相互通信代价与物理排布紧密相关,远端单元通信带宽远低于近端单元通信带宽,将计算通信简单地均分给不同的单元往往会造成数据传输代价不均衡,导致整体性能降低。为了解决在异构系统中部署多模型的问题,梁云副教授团队提出利用分组映射结合遗传算法的方式寻找优化映射策略。首先,课题组提出将多模型中的算子进行打包分组,以组为单位在计算单元上映射,一般来说算力强的单元分到较大的组,算力弱的单元分到较小的组,从而平衡不同单元的延迟,通信量较大的组分到相邻单元,通信量较小的组分到远端单元。但是手工分组与映射十分困难,效率低,为此,课题组提出自动化设计方案,通过初始枚举随机分组并利用遗传算法不断局部优化分组从而提高分组与映射的最终性能,经过数轮迭代达到较好的整体延迟和功耗。该工作以《Memory and Computation Coordinated Mapping of DNNsonto Complex Heterogeneous SoC》为题发表(博士生郑思泽为第一作者,梁云副教授为通讯作者)。

九、空间式架构的综合工具

面向空间式架构加速器的自动综合,针对空间式架构的设计空间巨大,难以进行高效的设计空间探索,无法从应用直接自动综合到硬件的问题,梁云副教授团队提出了对数据流进行分解的技术,以降低探索复杂度,提升加速器性能并减少资源使用。团队从设计空间式架构的关键中间表示形式数据流出发,提出了数据流分解技术:在数据流中,每一个张量的数据具有自己独立的运动行为。根据空间式架构在存储模块和计算模块上的划分,可以进一步将张量的运动分解为两个低层次的中间表示形式,分别体现其访存顺序以及在运算阵列中的数据运动。这两个低层次中间表示形式与硬件具有高度的相似性,因此可以高效地定制其设计自动空间,实现错误设计的快速排除,降低探索开销的同时提升结果质量。基于上述技术,课题组实现了从张量应用快速完成设计空间探索,并生成空间式架构加速器硬件的自动综合工具。针对于二维卷积应用在FPGA上的实现,该自动综合工具可以根据FPGA平台的特征,在低层次中间表示中筛选出适合的设计子空间,从而自动生成资源占用少,计算效率高的加速器设计。该工作以《Rubick: a Synthesis Framework for Spatial Architectures via Dataflow Decomposition》为题发表(博士生罗梓璋为第一作者,梁云副教授为通讯作者)。

背景链接:

由电气电子工程师学会(IEEE)和美国计算机协会 (ACM)资助的设计自动化会议(DAC)一直被公认为设计自动化领域最重要的会议,在国际半导体技术界享有很高的学术地位和广泛的影响力。该会议为设计工程师、研究人员、工具开发商等提供了绝佳的交流、教育以及展览的机会。