6月22日至25日,第62届设计自动化会议(DAC 2025)在美国旧金山召开。在本次大会上,来自电子设计自动化(EDA)与集成电路设计领域的高校、公司及研究机构群英荟萃,分享了EDA技术的最新发展和广泛应用,讨论了本领域进一步发展的前景和方向。北京大学多位教师马宇飞、王宗巍等担任了DAC的程序委员会(TPC)成员。集成电路学院的十余位师生现场参加了本次大会,进行了汇报与交流。

参会师生合影

在本次大会上,北京大学集成电路学院/集成电路高精尖创新中心共有13篇论文入选,研究成果覆盖了芯片设计、体系架构、存算一体、设计自动化、软硬件协同等领域。相关介绍如下:

1.多目标双面时钟树综合算法

随着半导体器件尺寸缩放逼近物理极限,利用硅基板背面空间已成为未来集成电路发展的新趋势。目前已有多个研究通过改造现有后端工具,探索利用纳米硅通孔(nTSV)实现双面时钟树综合的潜力,但这些工作缺乏对设计资源分配和多目标优化的系统性考量。本工作提出了基于多目标优化的双面时钟树综合,包含分层时钟树布线、缓冲器与纳米硅通孔协同插入以及偏差微调等关键技术。结合设计空间探索方法,进一步提升了双面时钟树综合工具的设计能力,可以满足不同的实际设计需求。相比于当前最先进的设计方法,在开源的测试样例上,平均减少了55%的时钟延迟、 59%的时钟偏差、1%的缓冲器数量、20%的布线长度优化及31%的nTSV数量。该工作以《A Systematic Approach for Multi-objective Double-side Clock Tree Synthesis》为题发表(博士生江循为第一作者,林亦波研究员为通讯作者)。

2.基于控制流与数据访问优化的定制加速器生成

定制加速器通过硬件专用化提升片上系统(SoC)的性能。高层次综合(HLS)工具能够为给定内核自动生成加速器,但需要手动选择和提取应用中的加速算子。本文提出Cayman,首个支持端到端生成具有控制流与数据访问双重优化的高性能定制加速器的框架。Cayman基于分层程序表示自动选择硬件加速算子,该表示方法能够捕获具有通用控制流的候选算子。此外,Cayman通过专用处理器-加速器接口实现数据访问加速优化。框架进一步引入创新的加速器合并机制以生成可复用加速器模块。在各类基准测试中的实验表明,Cayman相比现有工作取得8.0倍至14.4倍的性能优势。该工作以《Cayman: Custom Accelerator Generation with Control Flow and Data Access Optimization》为题发表(博士生肖有为为第一作者,梁云教授为通讯作者)。

3.GPU加速RTL仿真工具

GPU加速的RTL仿真工具(GEM)是一项面向高速电路验证的创新工作,旨在解决传统RTL仿真在性能和可扩展性方面的瓶颈。现有基于CPU的RTL仿真器在处理大规模设计时效率低下,而尽管基于FPGA的仿真平台能够实现加速,其高昂的成本与部署复杂性限制了普及。已有的GPU加速尝试未能实现预期性能突破,根本原因在于电路逻辑的异构性与GPU的SIMT(单指令多线程)执行模型之间存在结构性冲突,导致线程分歧和内存访问不规律问题严重。针对上述挑战,林亦波研究员团队受FPGA/ASIC硬件仿真启发,提出了一种面向GPU高效执行的虚拟超长指令字(VLIW)架构。该架构专为CUDA平台设计,能够更好地适配GPU的执行模型,显著减少线程分歧带来的性能损耗。同时,团队还设计了一套类似FPGA CAD流程的自动映射流程,将RTL电路逻辑高效映射到该虚拟VLIW架构中,从源头解决不规则访存问题,释放GPU在RTL仿真任务中的潜能。实验结果表明,该方法在通用GPU硬件上相较于当前最优的CPU RTL仿真器可实现最高达64倍的加速效果。GEM的提出,不仅大幅提升了RTL仿真的执行效率,更以更具可及性的硬件方案推动了高性能电路验证的普及,为GPU驱动的RTL仿真探索了全新方向。该工作以《GEM: GPU-Accelerated Emulator-Inspired RTL Simulation》为题发表(北京大学博士生郭资政为第一作者)。

4.基于交替方向乘子法(ADMM)的布局布线协同优化

布局在超大规模集成电路(VLSI)物理设计中具有关键作用,尤其在优化布线能力方面。随着半导体制造技术的持续进步、集成度不断提高以及设计复杂度日益增长,布局阶段的布线拥塞管理变得极具挑战性。尽管现有技术普遍采用多种方法来提升布线能力,但这些方法往往缺乏理论指导,或割裂了布局优化与布线优化之间的内在联系。本文提出RUPlace——一种基于交替方向乘子法(ADMM)的布局布线协同优化工具。通过融合瓦瑟斯坦距离与双层优化技术,本方法构建了全局布线与增量布局交替运行的统一拥塞优化框架。此外,我们创新性地提出了一种基于单元膨胀的简洁高效全局布局模型,采用凸规划方法求解最优膨胀比例。在CircuitNet和Chipyard开源工业基准测试集上的实验表明:相较于OpenROAD、Xplace 2.0和DREAMPlace 4.1等主流工具,RUPlace在保持线长与运行时竞争力的同时,能实现更优异的拥塞优化效果。该工作以《RUPlace: Optimizing Routability via Unified Placement and Routing Formulation》为题发表(博士生陈一帆为第一作者,林亦波研究员为通讯作者)。

5.协同优化的Die级别布线算法

随着现代集成电路设计规模的不断增大,由多个具有多个超级逻辑区域(SLR,也叫Die)的FPGA元件组成的多FPGA系统在现代集成电路的仿真中扮演了越来越重要的作用。在每个FPGA内部的布局布线之前,需要完成在系统层的布线和时分复用率分配。然而,传统的系统层布线算法大多关注FPGA层的布线,而忽略Die级别的布线,从而导致无法在系统层有效优化设计性能。针对这一难题,林亦波研究员团队提出了协同优化的Die级别布线算法。该算法通过拥塞-延迟平衡的初始布线和基于拉格朗日松弛的多线程时分复用率分配算法,有效地在Die级别高效完成了布线。结果表明,与现有最先进方法对比,该算法能够以5.761倍加速比减小7.6%的关键连接延迟。该工作以《Synergistic Die-Level Router for Multi-FPGA System with Time-Division Multiplexing Optimization》为题发表(博士生王嘉睿为第一作者,林亦波研究员为通讯作者)。

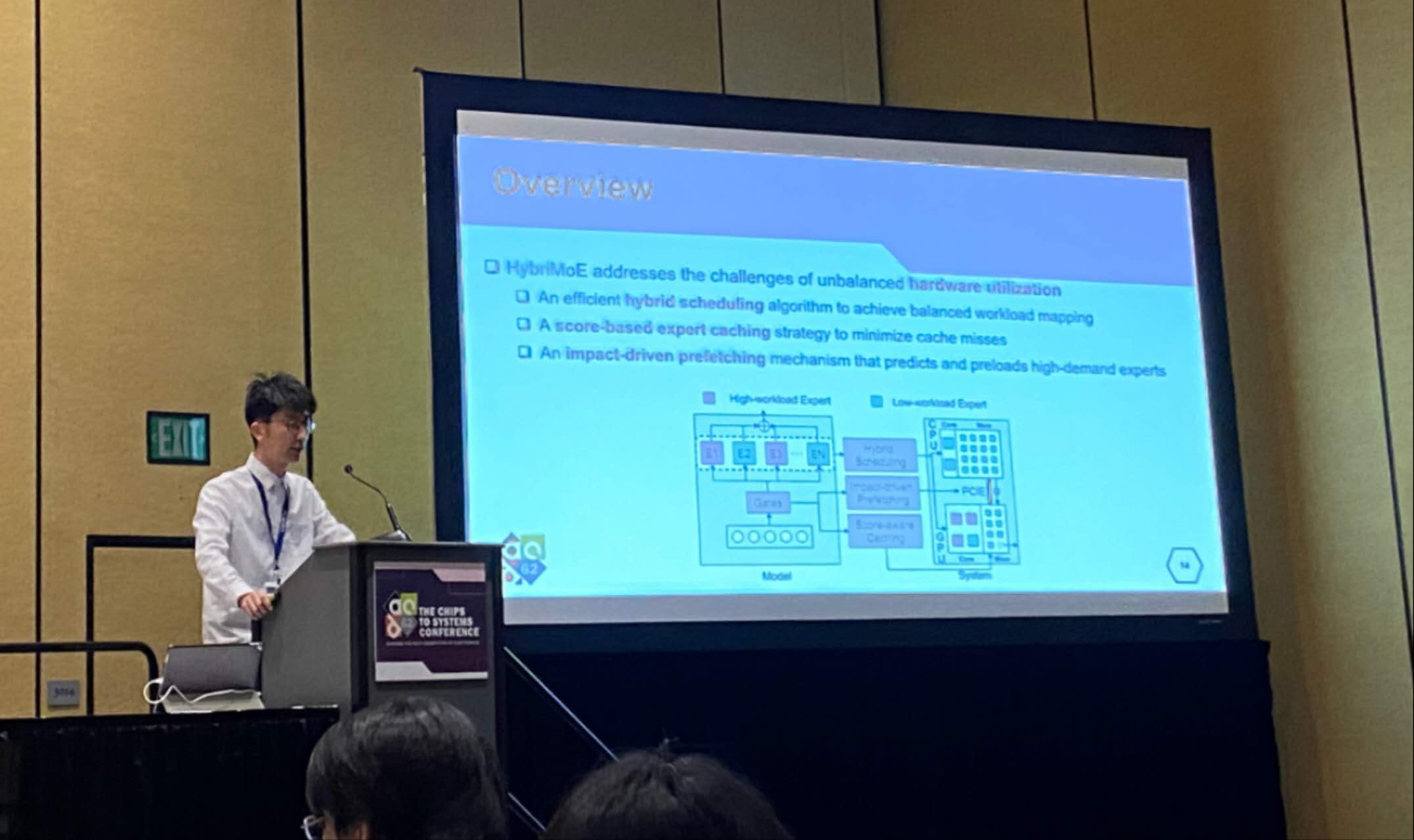

6.混合专家模型推理加速

混合专家模型(Mixture of Experts,MoE)已经成为了大语言模型的主流架构,但在边缘端设备上部署时面临权重存储需求过高的问题,需要将专家权重卸载至更低级存储,从而产生巨大的数据传输开销。部分工作尝试构建CPU-GPU协同的异构系统,使用CPU进行部分计算,降低模型权重加载到GPU上的传输开销。然而,现有的方法采用了固定的映射模式,在面对具有高度不稳定性的专家激活时,存在任务分配不均资源利用率较低的问题。针对这一挑战,李萌研究员团队提出了一种名为HybriMoE的CPU-GPU混合推理框架。HybriMoE框架通过三个核心技术创新解决了MoE推理过程中激活模式不稳定、负载分配不均的问题:(1)动态层内调度策略,有效平衡CPU和GPU的负载;(2)基于影响驱动的层间预取算法,优先预加载后续层中预期带来较大效益的专家;(3)基于专家评分的缓存管理策略,减少专家激活不稳定性带来的缓存未命中。实验结果表明,相较于现有最先进的混合推理框架,HybriMoE在预填充阶段平均获得了1.33倍的速度提升,在解码阶段则达到1.70倍的提升。该工作以《HybriMoE: Hybrid CPU-GPU Scheduling and Cache Management for Efficient MoE Inference》为题发表(北京大学博士生仲书璋为第一作者,李萌研究员为通讯作者)。

7.统一存内计算和搜索架构加速长文本大模型推理

基于Transformer架构的大语言模型(LLM)在自然语言处理任务中取得了显著成功,但是在对话系统、内容创作和文档摘要等需要处理超长序列的应用中,LLM的推理受限于KV缓存(KV cache)的高存储和计算开销,现有的基于存内计算加速器尽管引入了KV cache剪枝技术,但仅支持固定的静态剪枝或者动态剪枝,导致精度下降或者计算能效受限。针对上述调整,通过算法和硬件协同设计优化,提出支持动静态KV cache剪枝的统一存内计算和搜索架构(UniCAIM),并基于新型非易失性存储器FeFET硬件实现,可以实现O(1)时间复杂度的高效动态KV cache剪枝,以及基于积累相似度分数的灵活静态KV cache剪枝,在电路层相比现有存内计算加速器降低8.2∼831倍的面积-能量-延迟乘积,同时在应用层保持与稠密注意力计算相当的高精度,展现了其在长上下文LLM推理中的巨大潜力。该工作以《UniCAIM: A Unified CAM/CIM Architecture with Static-Dynamic KV Cache Pruning for Efficient Long-Context LLM Inference》为题发表(北京大学博士生徐伟凯和硕士生曾文轩为共同第一作者,黄如教授和李萌研究员为共同通讯作者)。

8.大语言模型的硬件容错

高效大语言模型推理的需求催生了专用加速器的发展。然而由于老化、工艺涨落等因素,这些加速器易发生硬件故障。现有设计通常预留较大的电压裕度或采用基于算法的容错(ABFT)技术来确保大模型推理的正确性。然而并非所有硬件故障都会影响模型输出结果,传统方案因此引入了较高的计算和能耗开销。为实现可靠且高效的大模型推理,李萌研究员-王润声教授团队提出了一种名为ReaLM的算法/电路协同设计框架。该架构首次通过大规模误差注入实验,系统地表征了大模型的容错特性。基于此,该框架提出了一种统计ABFT策略,该策略充分利用大模型的容错特性,仅针对关键错误触发恢复机制,来最大程度避免不必要的纠错开销。此外还设计了动态错误检测电路,以支持低成本的在线错误统计信息的收集。大量实验表明,在仅增加1.42%电路面积和1.79%功耗开销的情况下,ReaLM框架显著提高的大模型的可靠性。与现有方法相比,ReaLM在不同工作电压下均能显著降低纠错成本,并在保证大模型性能的前提下,将系统能效提升高达35.83%。该工作以《ReaLM: Reliable and Efficient Large Language Model Inference with Statiatical Algorithm-Based Fault Tolerance》为题发表(博士生解同为第一作者,李萌研究员为通讯作者)。

9.基于推测解码的语音识别加速框架SpecASR

基于大语言模型(LLM)的自动语音识别(ASR)由于具有较高的识别准确率和增强的多方言支持度,近年来受到了广泛关注。然而,LLM的高解码延迟对实时ASR的要求提出了挑战。尽管推测解码已经被探索以获得更好的解码效率,但其忽略了ASR任务的关键特性,只获得了有限的加速比。为了进一步降低实时ASR的延迟,李萌研究员团队提出了一种新的专门针对ASR的推测解码框架SpecASR。这一框架基于他们的核心观察开发,即ASR解码是音频条件化的,这导致小参数模型和大参数模型即使在中间解码步骤中输出不匹配,整体的输出对齐度很高。基于此,SpecASR提出自适应的草案序列生成过程,动态修改草稿序列长度,最大化验证接受数量。SpecASR进一步提出了草稿序列回收策略,对验证未通过的草稿序列进行再利用,以减少草稿ASR模型延迟。此外,李萌研究员团队还提出了一种两阶段稀疏词元树生成算法,以平衡草稿和目标模型间的延迟。在不损失识别准确率的情况下,SpecASR相比基线自回归解码和推测解码分别获得了3.04×-3.79×和1.25×-1.84×的加速。该工作以《SpecASR: Accelerating LLM-based Automatic Speech Recognition via Speculative Decoding》为题发表(博士生韦临烨为第一作者,李萌研究员为通讯作者)。

10.子图神经网络加速器

传统图神经网络(GNN)的表达能力等价于1阶Weisfeiler-Lehman测试,在一些场景下难以满足需求。子图GNN(Subgraph GNN)是一种新型GNN模型。一些研究工作已经证明子图GNN的表达能力能够达到3阶Weisfeiler-Lehman测试,在增强 GNN 表达能力方面非常有前景。但子图GNN需要分别处理大量独立且不规则的子图,这给硬件部署带来了重大挑战。在本研究中,北大团队提出了 3D-SubG,这是一种用于子图 GNN 的 3D 堆叠式近存/存内混合处理加速器。通过混合键合封装技术,逻辑芯片与 DRAM 芯片进行 3D 堆叠,以实现高度并行的内存访问。逻辑芯片采用基于存内计算的图加速引擎,以提高计算密度并减少数据传输。还提出了一种比特级非零值聚集方法以利用图的稀疏性,一种子图映射策略用于平衡工作负载,以及一种分布式全局池化方法以减少块间数据移动。实验结果表明,与 RTX 3090Ti 相比,3D-SubG 在性能上平均提升了 146.11 倍,在面积效率上提升了 934.18 倍,在能效上提升了 1171.80 倍。该工作以《3D-SubG: A 3D Stacked Hybrid Processing Near/In-Memory Accelerator for Subgraph GNNs》为题发表(博士生李国祥为第一作者,马宇飞研究员为通讯作者)。

11.高斯泼溅部署的硬件加速器

高斯泼溅模型(Gaussian Splatting,GS)是新视角生成(NVS)以及三维渲染任务的新兴主流算法,拥有渲染速度快、图形质量高等一系列优点。但由于算法中α-混合过程对渲染顺序的强依赖,以及高斯椭球大小对最大并行度的限制,高斯泼溅在渲染和训练过程中存在着并行低效,中间存储过多的问题。在本研究中,北京大学研究团队提出了Local-GS,一种通过重构渲染训练数据路径,实现无顺序依赖高效并行高斯泼溅部署的硬件加速器。在算法层面,Local-GS 引入神经网络参数,通过分段线性拟合高斯椭球的遮挡可见性模拟渲染顺序,实现了无顺序依赖的高效渲染-训练数据流;在架构层面,加速器利用重构后的数据流,实现了以高斯椭球为单位的工作负载调度,极大提高了硬件利用率;在电路层面,Local-GS 通过定制化的交叠测试单元(ITUs)和光栅化核心(Rasterization Cores)实现了对计算中间数据的有效利用,减轻了边缘端部署的存储压力。实验结果表明,Local-GS 比边缘端GPU(Jetson NX)的渲染和训练速度提升了约40倍;相比目前最先进的高斯泼溅加速器,Local-GS 实现了4.7倍的效率提升。文章以《Local-GS: An Order-Independent Gaussian Splatting Training Accelerator Exploiting Splat Locality》为题发表(博士生孙奕扬为第一作者,贾天宇研究员为通讯作者)

12.面向边缘端多模态大模型的多核异构CPU扩展

多模态大模型(MLLM)在传统大模型的推理能力上加入了跨模态的感知能力,因此在边缘端具有广阔的应用前景,例如:自动驾驶、具身智能、AR/VR等。然而,边缘端多模态大模型需要在受限的硬件资源下实现快速实时响应。CPU扩展方案通过增加扩展指令和协处理器能够在增强CPU并行计算能力的同时,继承原有软件工具链,因此是合适的边缘硬件平台。本文对MLLM应用进行了细致分析。之后,针对MLLM中需求差异的两种算子GEMM和GEMV分别设计了异构的、基于脉动阵列和sram 存内计算(Compute-In-Memory)的协处理器扩展,并集成进多核系统中。针对不同输出长度下的负载差异,设计了带宽资源管理方案提高异构核的利用率。针对激活通道中的离群值特性,又提出了激活感知的权重剪枝方案,进一步减少推理阶段带宽需求,提升整体性能。该工作以《EdgeMM: Multi-Core CPU with Heterogeneous AI-Extension and Activation-aware Weight Pruning for Multimodal LLMs at Edge》为题发表(博士生白康博为第一作者,贾天宇助理教授为通讯作者)

13.基于三维堆叠的存算一体大模型推测解码加速架构

大模型的解码过程面临两大瓶颈:从算法角度看,其自回归特性导致单步解码生成一个令牌(token)就需要加载全部模型参数;从硬件角度看,传统二维存储方案提供的带宽极为有限。针对上述问题,北京大学叶乐课题组提出一种名为3D-TokSIM的跨堆栈大模型推理加速架构,该架构通过在逻辑芯片上堆叠三维DRAM以实现更高效的存储访问,同时融合推测解码算法在单步解码过程中并行验证多个猜测的token以减少总解码步数,并借助存内计算(CIM)加速逻辑芯片上多token的并行计算。定制化设计的CIM采用令牌静止数据流,减少逻辑芯片上的数据搬运,平衡其访存与计算需求。进一步地,该工作通过精细的数据流优化,显著降低了逻辑芯片对缓存的需求,这使得在有限的芯片面积内能够配置更多的CIM资源,进而实现更高的推测解码并行度。相较于RTX3090 GPU和采用脉动阵列加速的三维堆叠架构,3D-TokSIM实现了15.1倍和1.5倍的解码速度提升与324倍和6.4倍的能效提升。该工作以《3D-TokSIM: Stacking 3D Memory with Token-Stationary Compute-in-Memory for Speculative LLM Inference》为题发表,(博士生赵文涛为第一作者,贾天宇研究员和叶乐教授为通讯作者)。